M65881AFP

5. FsoCKO

FsoCKO is clock output pin of 1fso frequency. The output is

Refer to the following Chapter 6. in detail.

6. FsoI, SFLAG

M65881AFP synchronizes in clock input from the external source devices. So it makes synchronized operation between source devices or another M65881AFP ( in case of Multi channel Operation ).

The primary side operation ( input side of sampling rate converter ) are synchronized in LRCK, and the secondary side operation ( output side of sampling rate converter ) are synchronized in FsoI. M65881AFP detects rise edge of these synchronized clock in normal operation, and the M65881AFP does operation of resynchronization in case that the cycle has changed.

In addition, the M65881AFP

While

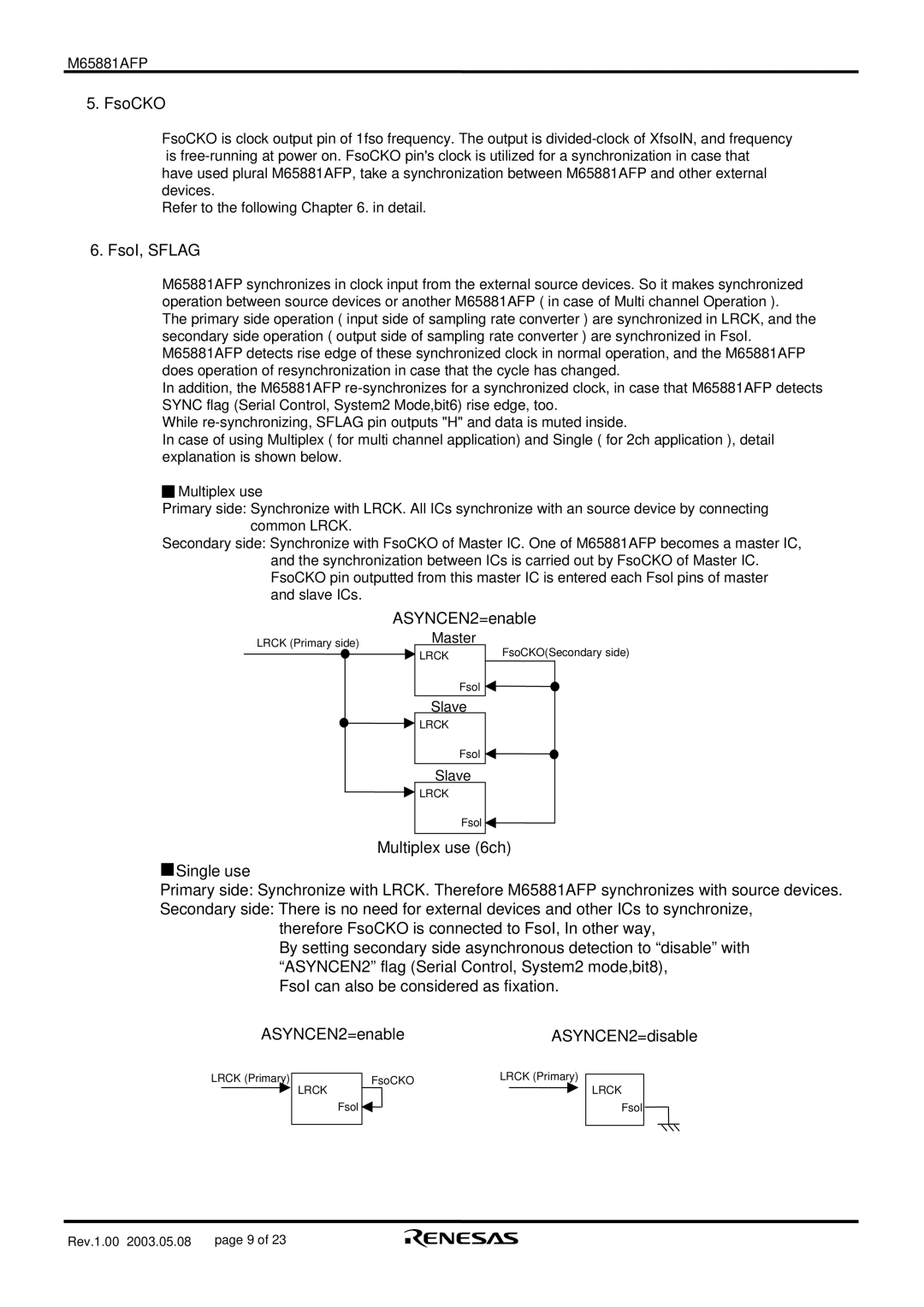

In case of using Multiplex ( for multi channel application) and Single ( for 2ch application ), detail explanation is shown below.

![]()

![]() Multiplex use

Multiplex use

Primary side: Synchronize with LRCK. All ICs synchronize with an source device by connecting common LRCK.

Secondary side: Synchronize with FsoCKO of Master IC. One of M65881AFP becomes a master IC, and the synchronization between ICs is carried out by FsoCKO of Master IC. FsoCKO pin outputted from this master IC is entered each Fsol pins of master and slave ICs.

ASYNCEN2=enable

LRCK (Primary side) | Master |

|

| FsoCKO(Secondary side) | |

| LRCK | |

|

| |

| Fsol |

|

| Slave |

|

| LRCK |

|

| Fsol |

|

| Slave |

|

| LRCK |

|

| Fsol |

|

Multiplex use (6ch)

![]()

![]() Single use

Single use

Primary side: Synchronize with LRCK. Therefore M65881AFP synchronizes with source devices.

Secondary side: There is no need for external devices and other ICs to synchronize, therefore FsoCKO is connected to FsoI, In other way,

By setting secondary side asynchronous detection to “disable” with “ASYNCEN2” flag (Serial Control, System2 mode,bit8),

FsoI can also be considered as fixation.

ASYNCEN2=enable | ASYNCEN2=disable |

LRCK (Primary)

LRCK | FsoCKO | LRCK (Primary) |

| ||

|

| |

Fsol |

|

|

|

|

|

LRCK

Fsol ![]()

![]()

Rev.1.00 2003.05.08 | page 9 of 23 |