M65881AFP

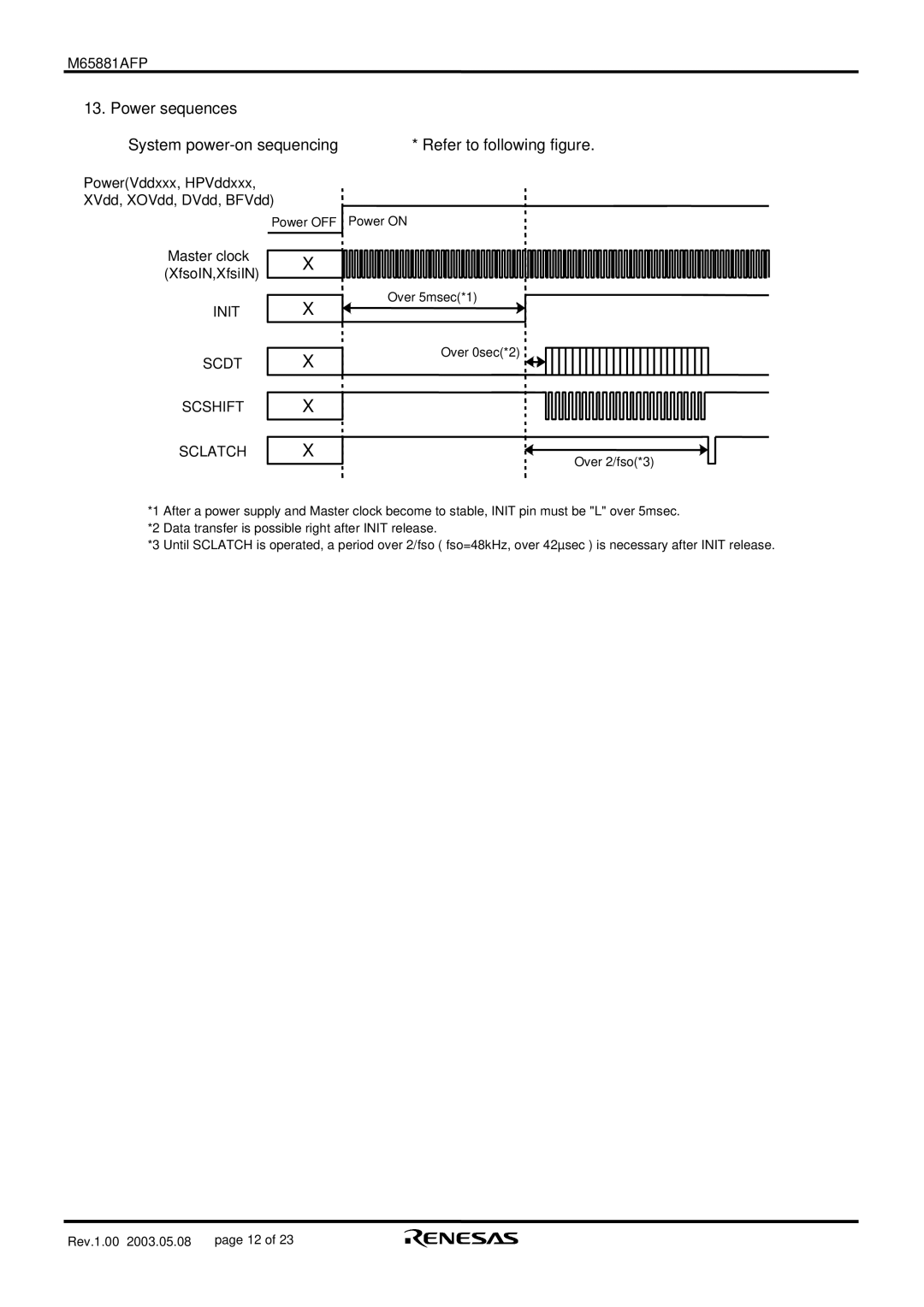

13. Power sequences

System | * Refer to following figure. |

Power(Vddxxx, HPVddxxx,

XVdd, XOVdd, DVdd, BFVdd)

Power OFF ![]() Power ON

Power ON

Master clock (XfsoIN,XfsiIN)

INIT

SCDT

SCSHIFT

SCLATCH

X

X

X

X

X

Over 5msec(*1)

Over 0sec(*2) ![]()

Over 2/fso(*3)

*1 After a power supply and Master clock become to stable, INIT pin must be "L" over 5msec.

*2 Data transfer is possible right after INIT release.

*3 Until SCLATCH is operated, a period over 2/fso ( fso=48kHz, over 42µsec ) is necessary after INIT release.

Rev.1.00 2003.05.08 | page 12 of 23 |