3 SOFTWARE IMPLEMENTATION | |

|

|

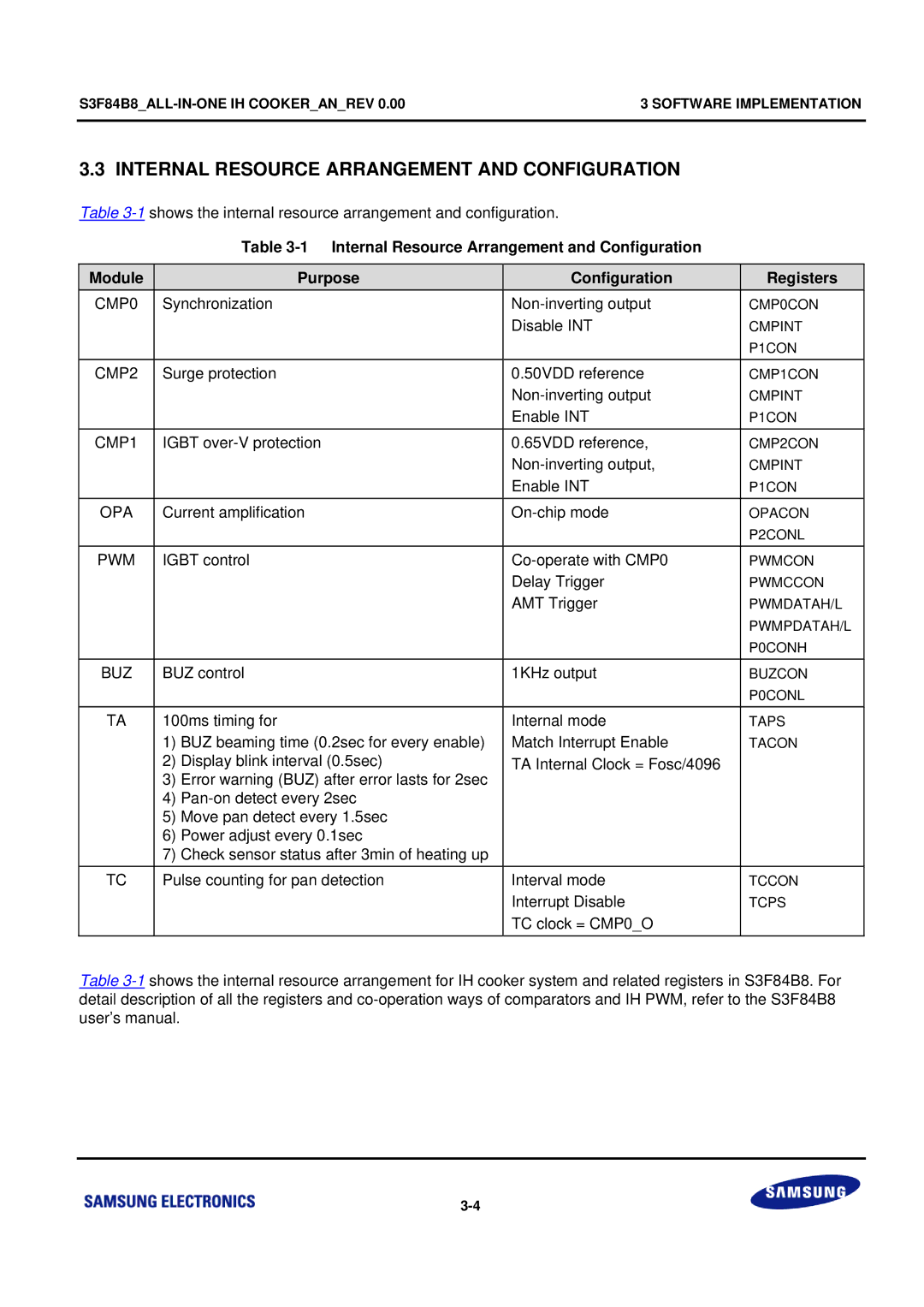

3.3 INTERNAL RESOURCE ARRANGEMENT AND CONFIGURATION

Table

Table

Module |

| Purpose | Configuration | Registers |

CMP0 | Synchronization | CMP0CON | ||

|

|

| Disable INT | CMPINT |

|

|

|

| P1CON |

|

|

|

| |

CMP2 | Surge protection | 0.50VDD reference | CMP1CON | |

|

|

| CMPINT | |

|

|

| Enable INT | P1CON |

CMP1 | IGBT | 0.65VDD reference, | CMP2CON | |

|

|

| CMPINT | |

|

|

| Enable INT | P1CON |

OPA | Current amplification | OPACON | ||

|

|

|

| P2CONL |

PWM | IGBT control | PWMCON | ||

|

|

| Delay Trigger | PWMCCON |

|

|

| AMT Trigger | PWMDATAH/L |

|

|

|

| PWMPDATAH/L |

|

|

|

| P0CONH |

BUZ | BUZ control | 1KHz output | BUZCON | |

|

|

|

| P0CONL |

TA | 100ms timing for | Internal mode | TAPS | |

| 1) | BUZ beaming time (0.2sec for every enable) | Match Interrupt Enable | TACON |

| 2) | Display blink interval (0.5sec) | TA Internal Clock = Fosc/4096 |

|

| 3) | Error warning (BUZ) after error lasts for 2sec |

|

|

| 4) |

|

| |

| 5) | Move pan detect every 1.5sec |

|

|

| 6) | Power adjust every 0.1sec |

|

|

| 7) | Check sensor status after 3min of heating up |

|

|

TC | Pulse counting for pan detection | Interval mode | TCCON | |

|

|

| Interrupt Disable | TCPS |

|

|

| TC clock = CMP0_O |

|

|

|

|

|

|

Table