Specifications

928-998-12

SELF-DIAGNOSIS Function

Items of Error History Mode Items and Contents

AEP, UK

Flexible Circuit Board Repairing

HK, SP, MY, AR, AUS, KR, JE

Diagrams

Table of Contents

Disassembly

Exploded Views

Section Servicing Note

Drawing OUT the Tray During Power OFF

Cleaning the Optical Pickup CD Player

Removing the Indication Plate FL

Service Position the Power Board

LED and Fluorescent Indicator Tube All Lit, Key Check Mode

Cold Reset

Hot Reset

Change-over of AM tuner Step between 9kHz and 10kHz

Aging Mode

Error History Display Mode

Reading the Mechanism Error History Display

Reading the BD Error History Display

IOP

JIG for Checking BD MD Board Waveform

TEO

Record Precedure

REC/PLAY

Checks Prior to Parts Replacement and Adjustments

Forced Reset

Main Board Component Side

Retry Cause Display Mode

Tuning +/MD/CD/TUNING +

Hexadecimal nBinary Conversion Table

Location of Parts and Controls

Section General

Front Panel

Page

Page

Section Disassembly

Case

Front Panel

Back Panel

Main Board and Power Transformer

CD Mechanism Deck

CD Base Unit

TRAY, Gear and CAM

Optical PICK-UP Section of CD KSS-213BA/F-NP

BD CD BOARD, Spindle Motor M101 and Sled Motor M102

MD Mechanism Deck

Set the shaft of Cam gear to

Over Write Head Optical PICK-UP of MD KMS-260B/J1N

Spindle Motor M901 and Sled Motor M902 MD

Setting the Test Mode

Section Test Mode

Precautions for USE of Test Mode

Exiting the Test Mode

Selecting the Test Mode

Display Contents Mark Group

MID

Operating the Continuous Playback Mode

Non-Volatile Memory Mode EEP Mode

OUT

Test Mode Displays

Functions of Other Buttons

Meanings of Other Displays

Section Electrical Adjustments

MD Section Parts Replacement and Adjustment

Precautions for Adjustments

Precautions for Checking Laser Diode Emissinon

Precautions for USE of Optical PICK- UP KMS-260B

Creating Continuously Recorded Disc

Checks Prior to Repairs

Temperature Compensation Offset Check

Laser Power Check

Specified Value

Focus Bias Check

Play Checking MO Error Rate Check

CD Error Rate Check

Self-Recording/playback Check

Laser Power Adjustment

Initial Setting of Adjustment Value

Temperature Compensation Offset Adjutment

Recording and Displaying the IOP Information

Traverse Adjustment

Check

Focus Bias Adjustment

Press the ENTER/YES R button, display EFB =

CD Auto Gain Control Output Level Adjustment

Error Rate Check

Auto Gain Control Output Level Adjustment

MO Auto Gain Control Output Level Adjustment

Curve Check

Adjusting Points and Connecting Points

CD Section

RF Level Check

HCD-MD373 Section Diagrams

Circuit Boards Location

Block Diagrams BD CD Section

HCD-MD373

BD MD /2

REC

D/A Converter

Main Section

BD CD Section

BD MD 2/2 Section

Waveforms BD CD Section

BD MD 1/2 Section

Main 3/3 Section

See page 40 for Circuit Boards Location

Printed Wiring Board BD CD Section

Main Board

Schematic Diagram BD CD Section

Printed Wiring Board BD MD Section

Semiconductor Location

Schematic Diagram BD MD /2

MD Digital Board

Schematic Diagram SP Section Printed Wiring Board SP Section

Printed Wiring Board Main Section

Schematic Diagram Main /3

See page 68 for IC Block Diagrams

HCD-MD373

HCD-MD373

Schematic Diagram MD Digital Section

See page 45 for Waveforms See page 67 for IC Block Diagrams

Printed Wiring Board MD Digital Section

Schematic Diagram AMP Section

Printed Wiring Board AMP Section

Schematic Diagram Panel Section

Printed Wiring Board Panel Section

Schematic Diagram Power Section

AEP, UK

Printed Wiring Board Power Section

Except AEP, UK Voltage Selector

Schematic Diagram Loading Section

Schematic Diagram BD Switch Section

Printed Wiring Board BD Switch Section

Printed Wiring Board Loading Section

IC Block Diagrams

BD MD Board 1/2 IC101 CXA2523AR

IC152 BH6511FS-E2

BD MD Board 2/2 IC121 CXD2654R

C103 CXA2568M-T6 MD Digital Board

BD CD Board IC101 CXD2587Q

IC153 LB1830M-S-TE-L

Main Board 1/3 IC302 MC14052B

Main Board 3/3 IC171 LB1641

Main Board 2/3 IC301 M62428AFP IC931 M62016L

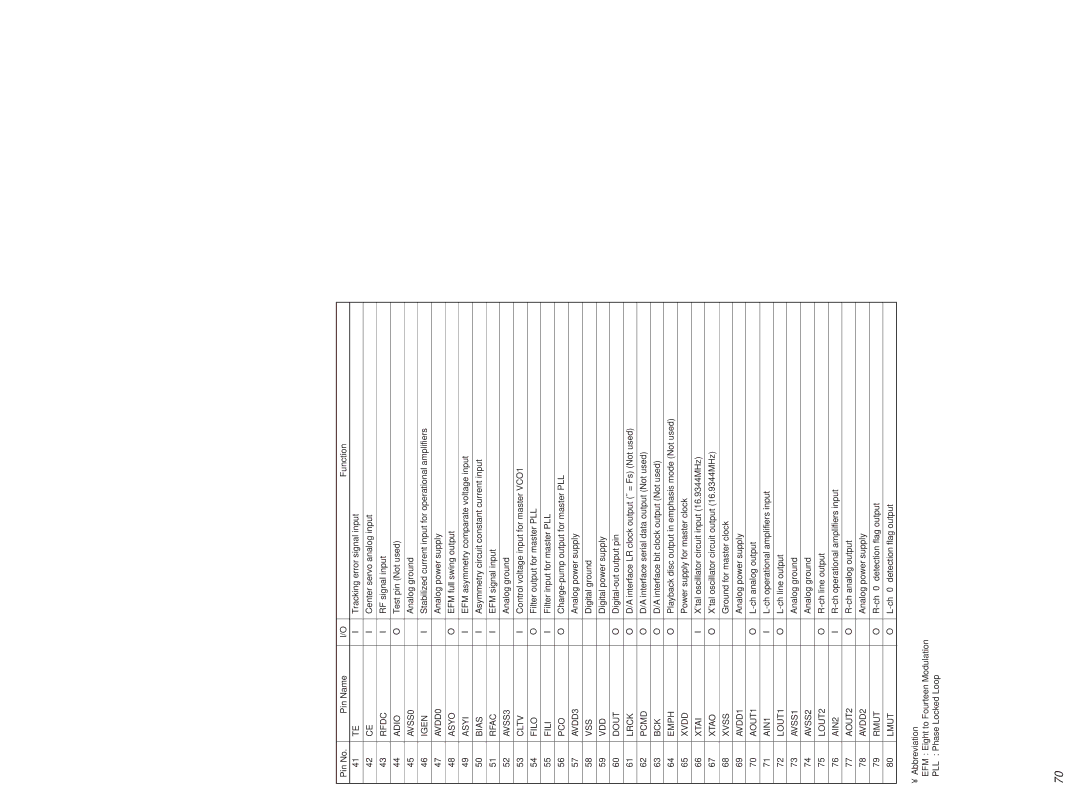

IC101 Digital Signal Processor CXD2587Q Bdcd board

IC PIN Functions

AVSS0

Rfdc

Adio

Igen

IC101 RF Amplifier CXA2523AR Bdmd board

MNT2 Xbusy

MNT0 FOK

MNT1 Shck

MNT3 Sloc

RFI

Mvci

Avdd

Avss

Spfd

FS4

Sprd

Fgin

IC501 Master Control M30620ECFP-A21 Main board

Tuned

CD-RESET

Stereo

ST-CE

Section Exploded Views

Case and Front Panel Section

Chassis Section

59 #3

113 110 107

MD Mechanism Deck MDM-5A

125 126 106 105

MD Base Unit MBU-5A

CD Mechanism Deck CDM55A-5SBD32

252 254

CD Base Unit BU-5SBD32

255 256 257 253 254

258 251

CD Mechanism Deck CDM55C-5BD32

352 354

CD Base Unit BU-5BD32

355 356 357 353 354

358 351

Section Electrical Parts List AMP

AMP BD CD

BD CD BD MD

2SJ278MYTR

BD MD MD Digital

Inductor Chip

2SK1764KYTR Resistor

MD Digital Loading Main

Main

Terminal BOARD, Ground

Ground Terminal

EP1

EP2

Description Remark R402 249-417-11

Panel BOARD, Complete

Indicator TUBE, Fluorescent

Panel

Jack LINE-IN

Panel Power

PIN, Connector 7P

Switch Voltage Selestor

TRANSFORMER, SUB Power

SWITCH, Push 1 KEY

SCREW,PRECISION +P

Hardware List

Screw +B

Memo

HCD-MD373 Revision History