BIOS Setup Utility![]() SY-7VCA2

SY-7VCA2

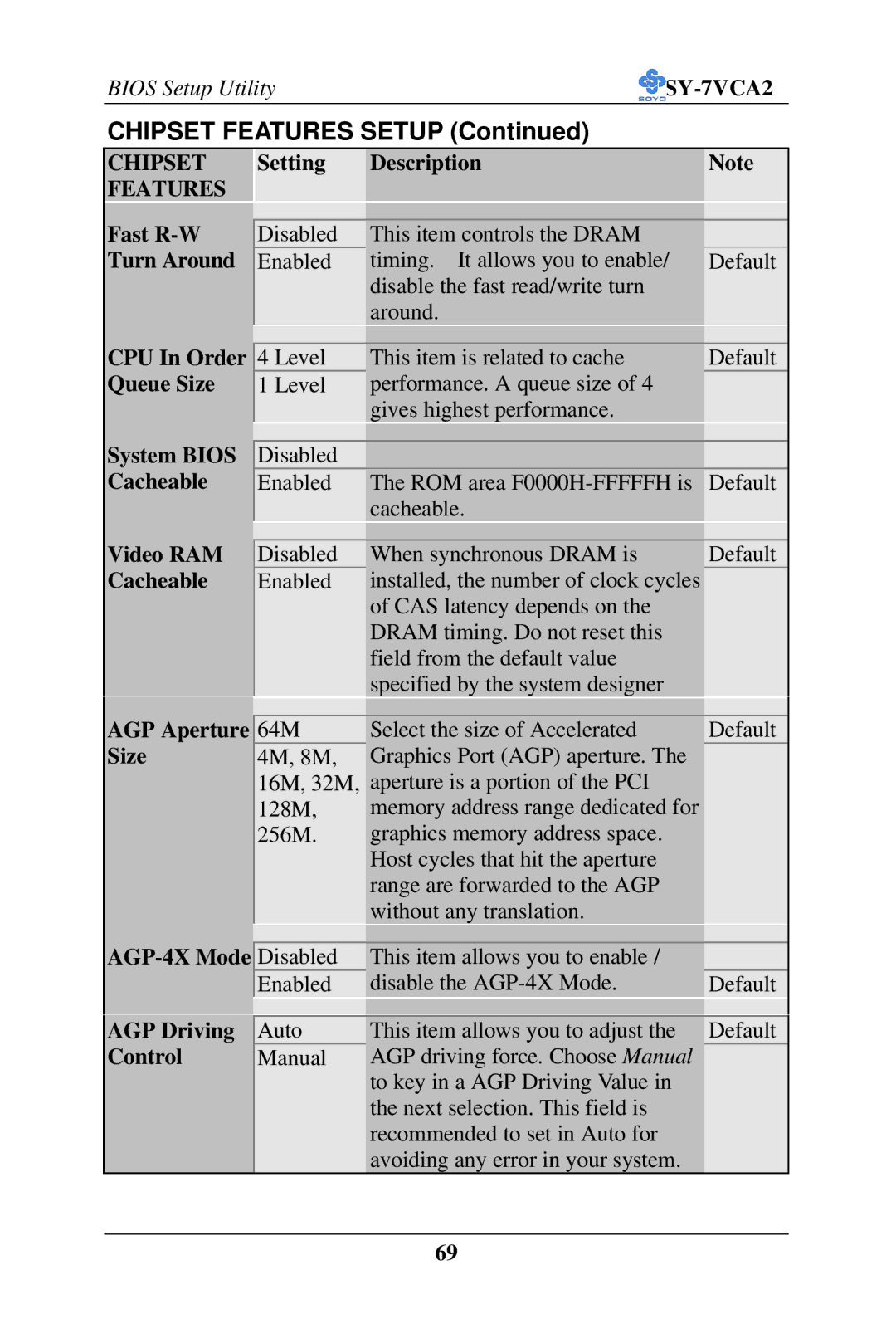

CHIPSET FEATURES SETUP (Continued)

CHIPSET |

| Setting | Description | Note |

FEATURES |

|

|

|

|

Fast |

|

|

|

|

| Disabled | This item controls the DRAM |

| |

Turn Around |

| Enabled | timing. It allows you to enable/ | Default |

|

|

| disable the fast read/write turn |

|

|

|

| around. |

|

CPU In Order |

|

|

|

|

| 4 Level | This item is related to cache | Default | |

Queue Size |

| 1 Level | performance. A queue size of 4 |

|

|

|

| gives highest performance. |

|

|

|

|

|

|

System BIOS Cacheable

Video RAM Cacheable

Disabled

Enabled | The ROM area | Default |

| cacheable. |

|

|

|

|

|

|

|

Disabled | When synchronous DRAM is | Default |

Enabled | installed, the number of clock cycles |

|

| of CAS latency depends on the |

|

| DRAM timing. Do not reset this |

|

field from the default value specified by the system designer

AGP Aperture Size

AGP-4X Mode

AGP Driving Control

|

|

|

|

|

| 64M | Select the size of Accelerated | Default |

|

| 4M, 8M, | Graphics Port (AGP) aperture. The |

|

|

| 16M, 32M, | aperture is a portion of the PCI |

|

|

| 128M, | memory address range dedicated for |

|

|

| 256M. | graphics memory address space. |

|

|

|

| Host cycles that hit the aperture |

|

|

|

| range are forwarded to the AGP |

|

|

|

| without any translation. |

|

|

|

|

|

|

|

| Disabled | This item allows you to enable / |

|

|

| Enabled | disable the | Default |

|

|

|

|

|

|

| Auto | This item allows you to adjust the | Default |

|

| Manual | AGP driving force. Choose Manual |

|

|

|

| to key in a AGP Driving Value in |

|

|

|

| the next selection. This field is |

|

|

recommended to set in Auto for avoiding any error in your system.

69