386SX, AR-B1376, AR-B1375 specifications

The Toshiba AR-B1375 and AR-B1376 are notable embedded computing solutions that incorporate the 386SX microprocessor architecture. Designed for various applications, these models focus on reliability, performance, and versatility, making them appealing choices for system integrators and developers.At the core of the AR-B1375 and AR-B1376 is the Intel 386SX microprocessor. This landmark processor marked a significant advancement in computing technology, introducing a 32-bit architecture while maintaining compatibility with 16-bit applications. The 386SX is known for its efficient processing capabilities, offering both multitasking support and enhanced memory management. It operates at clock speeds ranging typically from 16 MHz to 25 MHz, contributing to its effectiveness in running industrial applications.

One of the key features of the AR-B1375 and AR-B1376 systems is their modular architecture, which allows for easy customization and expansion. This modularity means users can tailor the hardware according to specific requirements, making it suitable for a wide range of applications such as automation, telecommunications, and embedded systems.

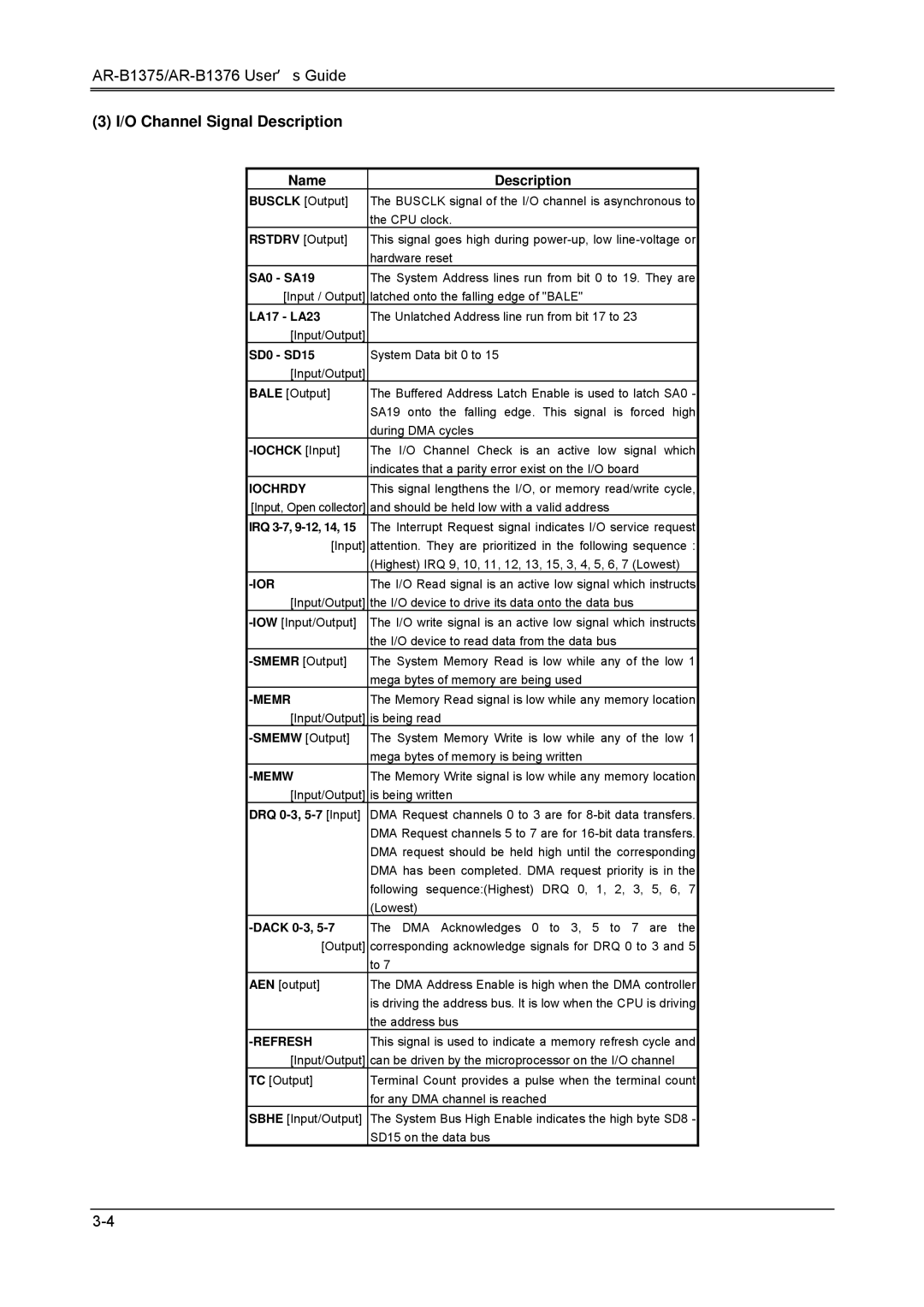

Both models support various I/O options, ensuring seamless integration with peripherals and external devices. They typically come equipped with serial and parallel ports, as well as support for modern interfaces like USB. The systems also feature onboard expansion slots, enabling the addition of further functionality, such as additional memory or specialized processing units.

In terms of memory, the AR-B1375 and AR-B1376 support a range of RAM configurations, allowing users to scale their systems based on the application demands. The inclusion of EPROM and EEPROM options also facilitates easy updates and programmability, which is crucial for embedded systems that often require firmware adjustments over time.

Moreover, these models are known for their robust thermal management features, which are essential in industrial environments where conditions can be harsh. This capability ensures stable performance and longevity, reducing the risk of system failures due to overheating or environmental factors.

To summarize, the Toshiba AR-B1375 and AR-B1376, coupled with the 386SX microprocessor, offer a blend of performance, flexibility, and reliability. Their modular design, extensive I/O support, and memory scalability make them ideal for a variety of embedded computing applications, placing them as commendable options in the world of industrial computing solutions. These systems not only exemplify Toshiba's commitment to innovation but also contribute significantly to the functionality of embedded technologies in a rapidly evolving industry.