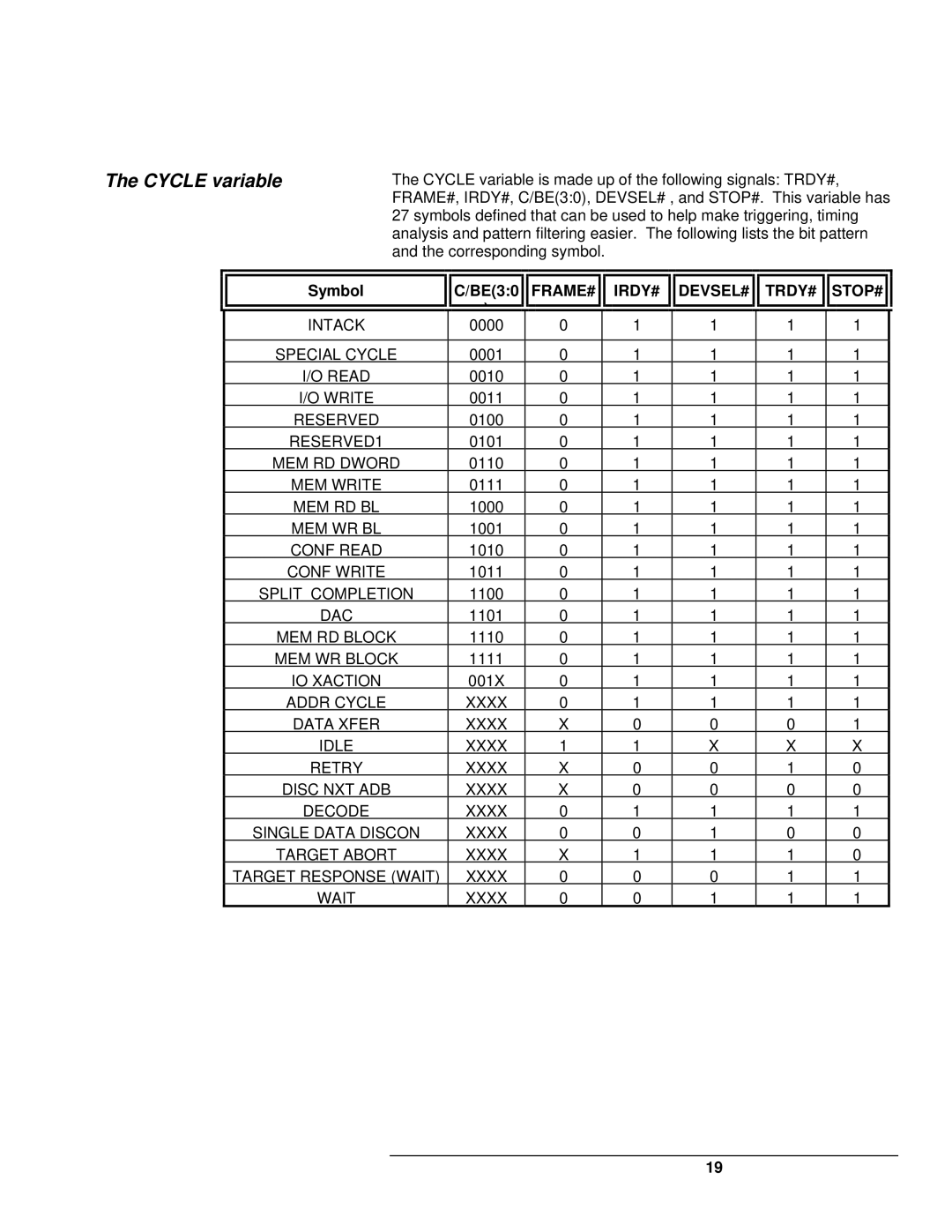

The CYCLE variable | The CYCLE variable is made up of the following signals: TRDY#, | |||||||

|

| FRAME#, IRDY#, C/BE(3:0), DEVSEL# , and STOP#. This variable has | ||||||

|

| 27 symbols defined that can be used to help make triggering, timing | ||||||

|

| analysis and pattern filtering easier. The following lists the bit pattern | ||||||

|

| and the corresponding symbol. |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| Symbol | C/BE(3:0 | FRAME# | IRDY# | DEVSEL# | TRDY# | STOP# |

|

|

| ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| INTACK | 0000 | 0 | 1 | 1 | 1 | 1 |

|

|

|

|

|

|

|

| |

| SPECIAL CYCLE | 0001 | 0 | 1 | 1 | 1 | 1 | |

|

| I/O READ | 0010 | 0 | 1 | 1 | 1 | 1 |

|

| I/O WRITE | 0011 | 0 | 1 | 1 | 1 | 1 |

|

| RESERVED | 0100 | 0 | 1 | 1 | 1 | 1 |

|

| RESERVED1 | 0101 | 0 | 1 | 1 | 1 | 1 |

| MEM RD DWORD | 0110 | 0 | 1 | 1 | 1 | 1 | |

|

| MEM WRITE | 0111 | 0 | 1 | 1 | 1 | 1 |

|

| MEM RD BL | 1000 | 0 | 1 | 1 | 1 | 1 |

|

| MEM WR BL | 1001 | 0 | 1 | 1 | 1 | 1 |

|

| CONF READ | 1010 | 0 | 1 | 1 | 1 | 1 |

|

| CONF WRITE | 1011 | 0 | 1 | 1 | 1 | 1 |

| SPLIT COMPLETION | 1100 | 0 | 1 | 1 | 1 | 1 | |

|

| DAC | 1101 | 0 | 1 | 1 | 1 | 1 |

| MEM RD BLOCK | 1110 | 0 | 1 | 1 | 1 | 1 | |

| MEM WR BLOCK | 1111 | 0 | 1 | 1 | 1 | 1 | |

|

| IO XACTION | 001X | 0 | 1 | 1 | 1 | 1 |

|

| ADDR CYCLE | XXXX | 0 | 1 | 1 | 1 | 1 |

|

| DATA XFER | XXXX | X | 0 | 0 | 0 | 1 |

|

| IDLE | XXXX | 1 | 1 | X | X | X |

|

| RETRY | XXXX | X | 0 | 0 | 1 | 0 |

|

| DISC NXT ADB | XXXX | X | 0 | 0 | 0 | 0 |

|

| DECODE | XXXX | 0 | 1 | 1 | 1 | 1 |

| SINGLE DATA DISCON | XXXX | 0 | 0 | 1 | 0 | 0 | |

| TARGET ABORT | XXXX | X | 1 | 1 | 1 | 0 | |

| TARGET RESPONSE (WAIT) | XXXX | 0 | 0 | 0 | 1 | 1 | |

|

| WAIT | XXXX | 0 | 0 | 1 | 1 | 1 |

19