VIP4 Overview

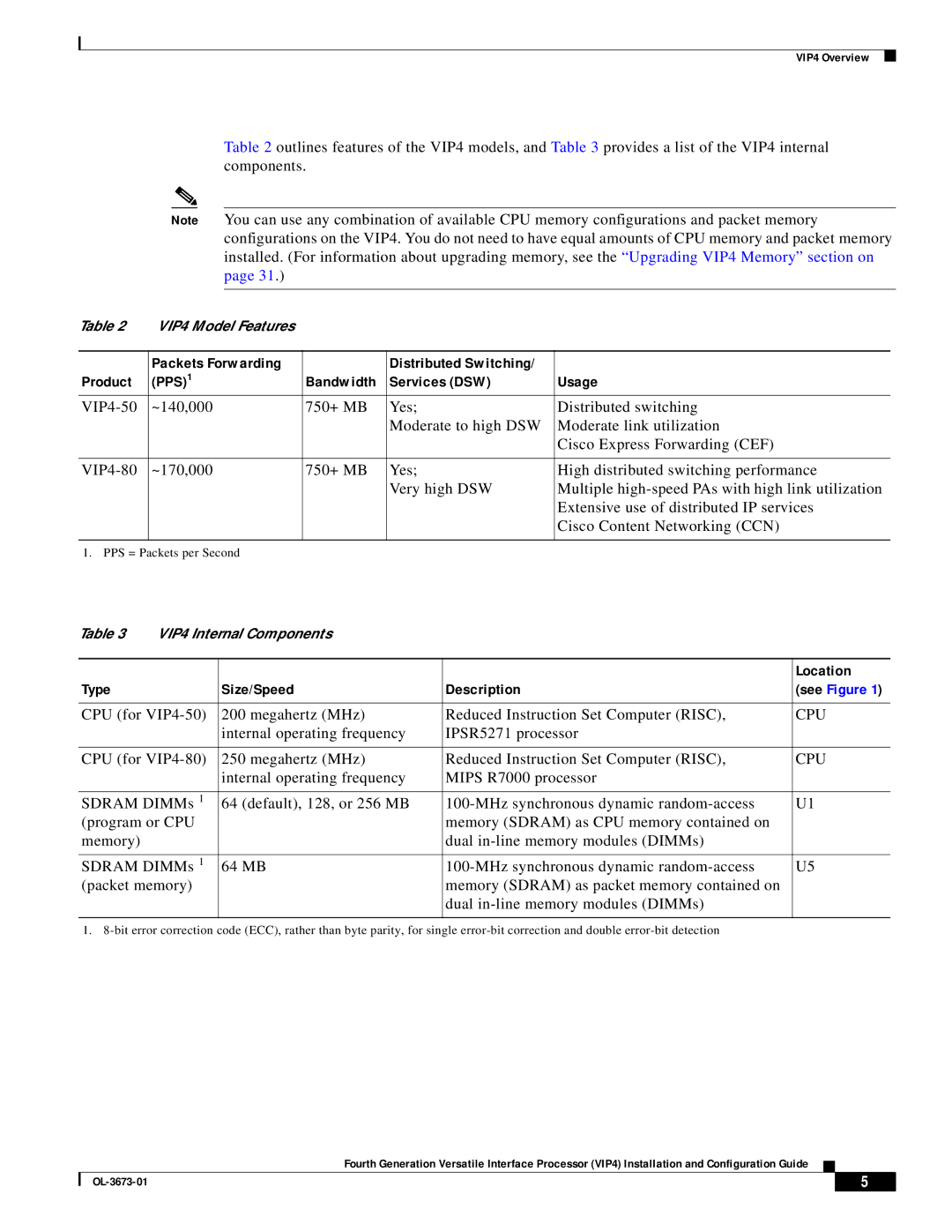

Table 2 outlines features of the VIP4 models, and Table 3 provides a list of the VIP4 internal components.

Note You can use any combination of available CPU memory configurations and packet memory configurations on the VIP4. You do not need to have equal amounts of CPU memory and packet memory installed. (For information about upgrading memory, see the “Upgrading VIP4 Memory” section on page 31.)

Table 2 | VIP4 Model Features |

|

|

|

|

|

|

|

|

| Packets Forwarding |

| Distributed Switching/ |

|

Product | (PPS)1 | Bandwidth | Services (DSW) | Usage |

~140,000 | 750+ MB | Yes; | Distributed switching | |

|

|

| Moderate to high DSW | Moderate link utilization |

|

|

|

| Cisco Express Forwarding (CEF) |

|

|

|

|

|

~170,000 | 750+ MB | Yes; | High distributed switching performance | |

|

|

| Very high DSW | Multiple |

|

|

|

| Extensive use of distributed IP services |

|

|

|

| Cisco Content Networking (CCN) |

|

|

|

|

|

1. PPS = Packets per Second |

|

|

| |

Table 3 | VIP4 Internal Components |

|

| |

|

|

|

|

|

|

|

|

| Location |

Type |

| Size/Speed | Description | (see Figure 1) |

|

|

|

| |

CPU (for | 200 megahertz (MHz) | Reduced Instruction Set Computer (RISC), | CPU | |

|

| internal operating frequency | IPSR5271 processor |

|

|

|

|

| |

CPU (for | 250 megahertz (MHz) | Reduced Instruction Set Computer (RISC), | CPU | |

|

| internal operating frequency | MIPS R7000 processor |

|

|

|

|

| |

SDRAM DIMMs 1 | 64 (default), 128, or 256 MB | U1 | ||

(program or CPU |

| memory (SDRAM) as CPU memory contained on |

| |

memory) |

|

| dual |

|

|

|

|

| |

SDRAM DIMMs 1 | 64 MB | U5 | ||

(packet memory) |

| memory (SDRAM) as packet memory contained on |

| |

|

|

| dual |

|

|

|

|

|

|

1.

Fourth Generation Versatile Interface Processor (VIP4) Installation and Configuration Guide

| 5 |

| |

|

|