HARDWARE

2.3MEMORY MAP

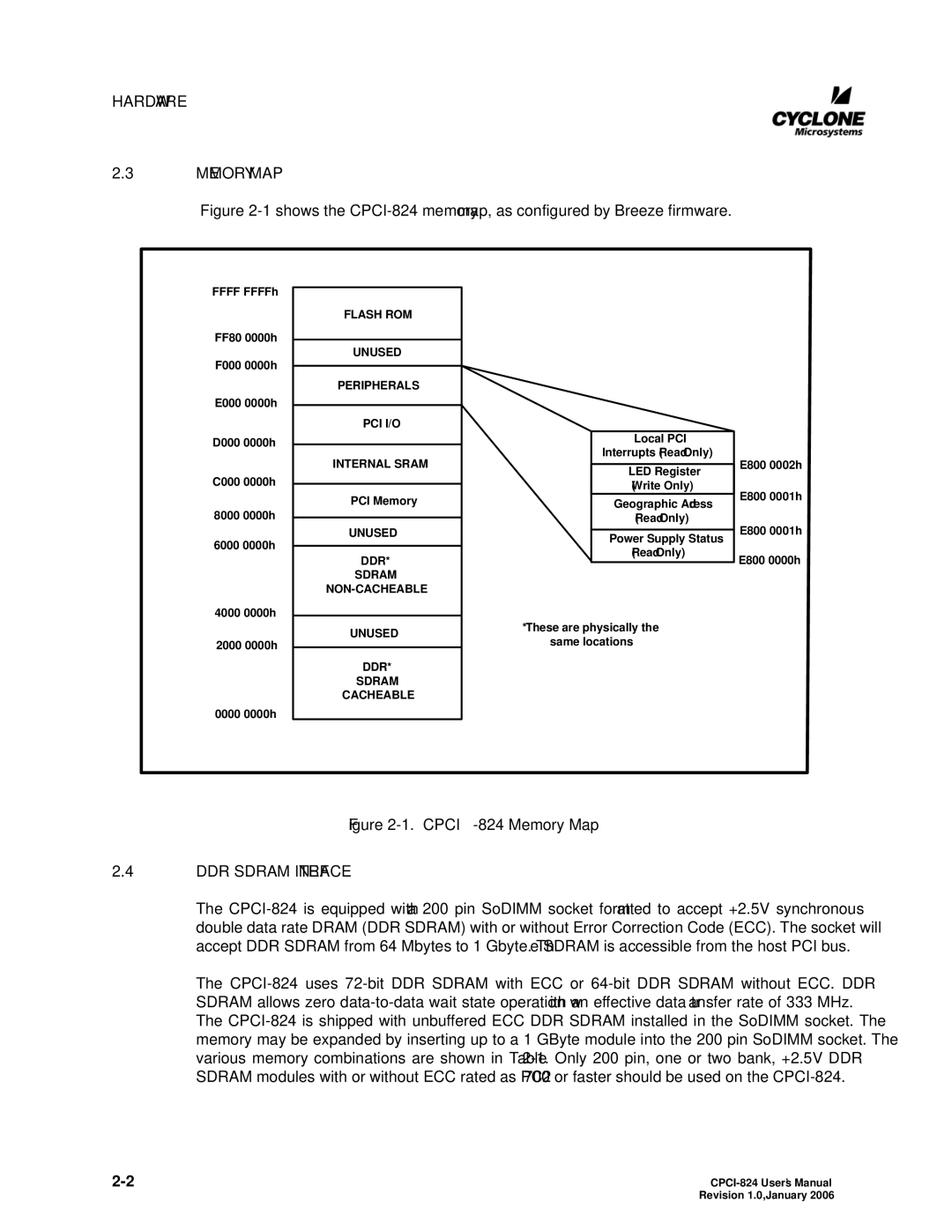

Figure 2-1 shows the CPCI-824 memory map, as configured by Breeze firmware.

FFFF FFFFh

FF80 0000h F000 0000h

E000 0000h

D000 0000h

C000 0000h

8000 0000h

6000 0000h

4000 0000h

2000 0000h

0000 0000h

FLASH ROM

UNUSED

PERIPHERALS

PCI I/O

INTERNAL SRAM

PCI Memory

UNUSED

DDR*

SDRAM

NON-CACHEABLE

UNUSED

DDR*

SDRAM

CACHEABLE

Local PCI

Interrupts (Read Only)

LED Register

(Write Only)

Geographic Address

(Read Only)

Power Supply Status

(Read Only)

*These are physically the same locations

E800 0002h

E800 0001h

E800 0001h

E800 0000h

Figure 2-1. CPCI-824 Memory Map

2.4DDR SDRAM INTERFACE

The

The

| Revision 1.0, January 2006 |