CY62256

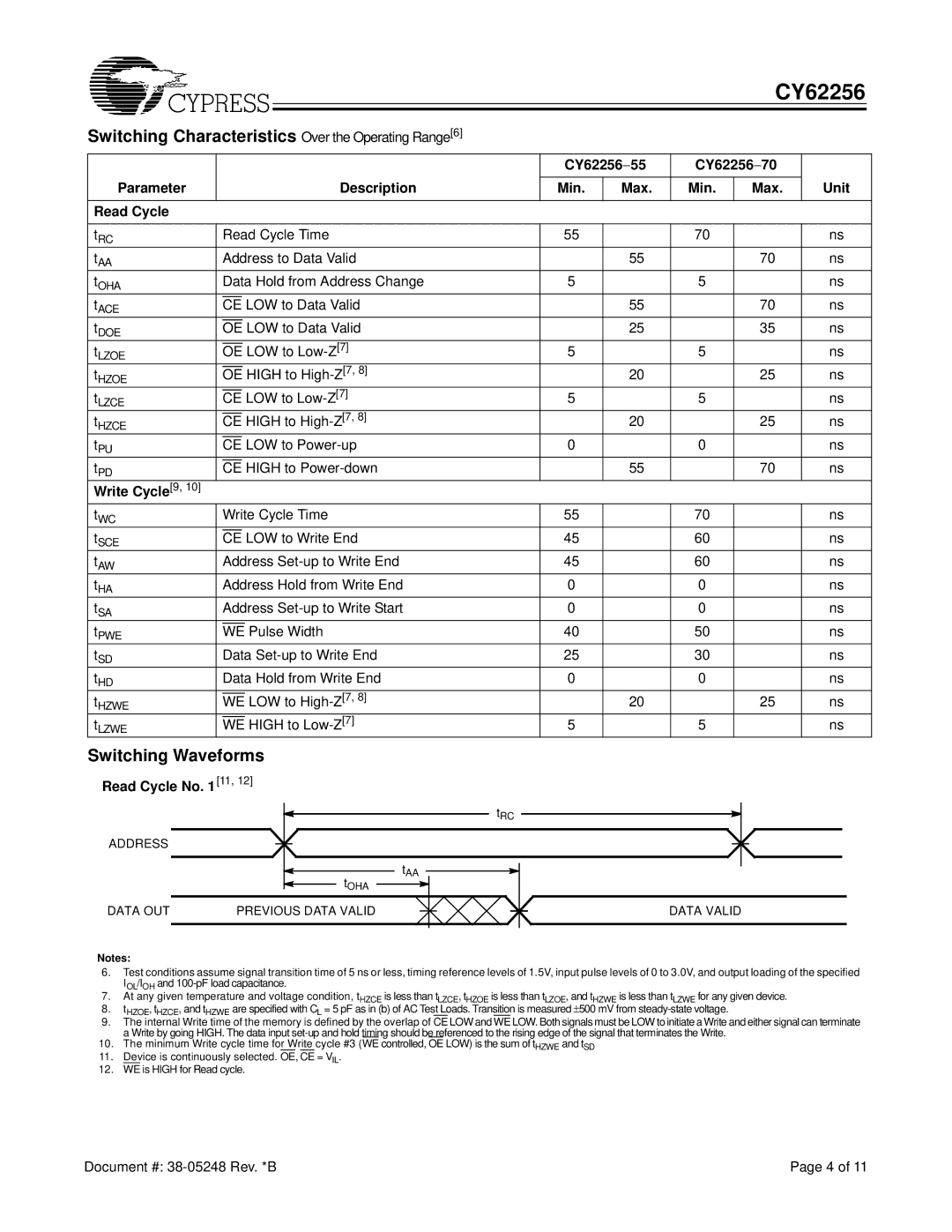

Switching Characteristics Over the Operating Range[6]

|

|

|

|

|

|

| CY62256− 55 | CY62256− 70 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

|

|

| Description | Min. | Max. | Min. | Max. | Unit | |

|

|

|

|

|

|

|

|

|

|

|

|

Read Cycle |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| ||||

tRC |

| Read Cycle Time | 55 |

| 70 |

| ns | ||||

tAA |

| Address to Data Valid |

| 55 |

| 70 | ns | ||||

tOHA |

| Data Hold from Address Change | 5 |

| 5 |

| ns | ||||

tACE |

|

|

|

| LOW to Data Valid |

| 55 |

| 70 | ns | |

| CE |

|

|

|

| ||||||

tDOE |

|

|

|

| LOW to Data Valid |

| 25 |

| 35 | ns | |

| OE |

|

|

| |||||||

tLZOE |

|

|

|

| LOW to | 5 |

| 5 |

| ns | |

| OE |

|

| ||||||||

tHZOE |

|

|

|

| HIGH to |

| 20 |

| 25 | ns | |

| OE |

|

| ||||||||

tLZCE |

|

|

| LOW to | 5 |

| 5 |

| ns | ||

| CE |

|

| ||||||||

tHZCE |

|

|

| HIGH to |

| 20 |

| 25 | ns | ||

| CE |

|

| ||||||||

tPU |

|

|

|

| LOW to | 0 |

| 0 |

| ns | |

| CE |

|

|

| |||||||

tPD |

|

|

|

| HIGH to |

| 55 |

| 70 | ns | |

| CE |

|

|

| |||||||

Write Cycle[9, 10] |

|

|

|

|

|

|

|

|

|

|

|

tWC |

| Write Cycle Time | 55 |

| 70 |

| ns | ||||

tSCE |

|

|

|

| LOW to Write End | 45 |

| 60 |

| ns | |

| CE |

|

|

| |||||||

tAW |

| Address | 45 |

| 60 |

| ns | ||||

tHA |

| Address Hold from Write End | 0 |

| 0 |

| ns | ||||

tSA |

| Address | 0 |

| 0 |

| ns | ||||

tPWE |

|

|

|

| Pulse Width | 40 |

| 50 |

| ns | |

| WE |

|

| ||||||||

tSD |

| Data | 25 |

| 30 |

| ns | ||||

tHD |

| Data Hold from Write End | 0 |

| 0 |

| ns | ||||

tHZWE |

|

|

|

| LOW to |

| 20 |

| 25 | ns | |

| WE |

|

| ||||||||

tLZWE |

|

|

|

| HIGH to | 5 |

| 5 |

| ns | |

| WE |

|

| ||||||||

Switching Waveforms

Read Cycle No. 1[11, 12]

tRC

ADDRESS

tAA

tOHA

DATA OUT | PREVIOUS DATA VALID |

Notes:

DATA VALID

6.Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified IOL/IOH and

7.At any given temperature and voltage condition, tHZCE is less than tLZCE, tHZOE is less than tLZOE, and tHZWE is less than tLZWE for any given device.

8.tHZOE, tHZCE, and tHZWE are specified with CL = 5 pF as in (b) of AC Test Loads. Transition is measured ± 500 mV from

9.The internal Write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a Write and either signal can terminate a Write by going HIGH. The data input

10.The minimum Write cycle time for Write cycle #3 (WE controlled, OE LOW) is the sum of tHZWE and tSD

11.Device is continuously selected. OE, CE = VIL.

12.WE is HIGH for Read cycle.

Document #: | Page 4 of 11 |