CY7C024AV/024BV/025AV/026AV

CY7C0241AV/0251AV/036AV

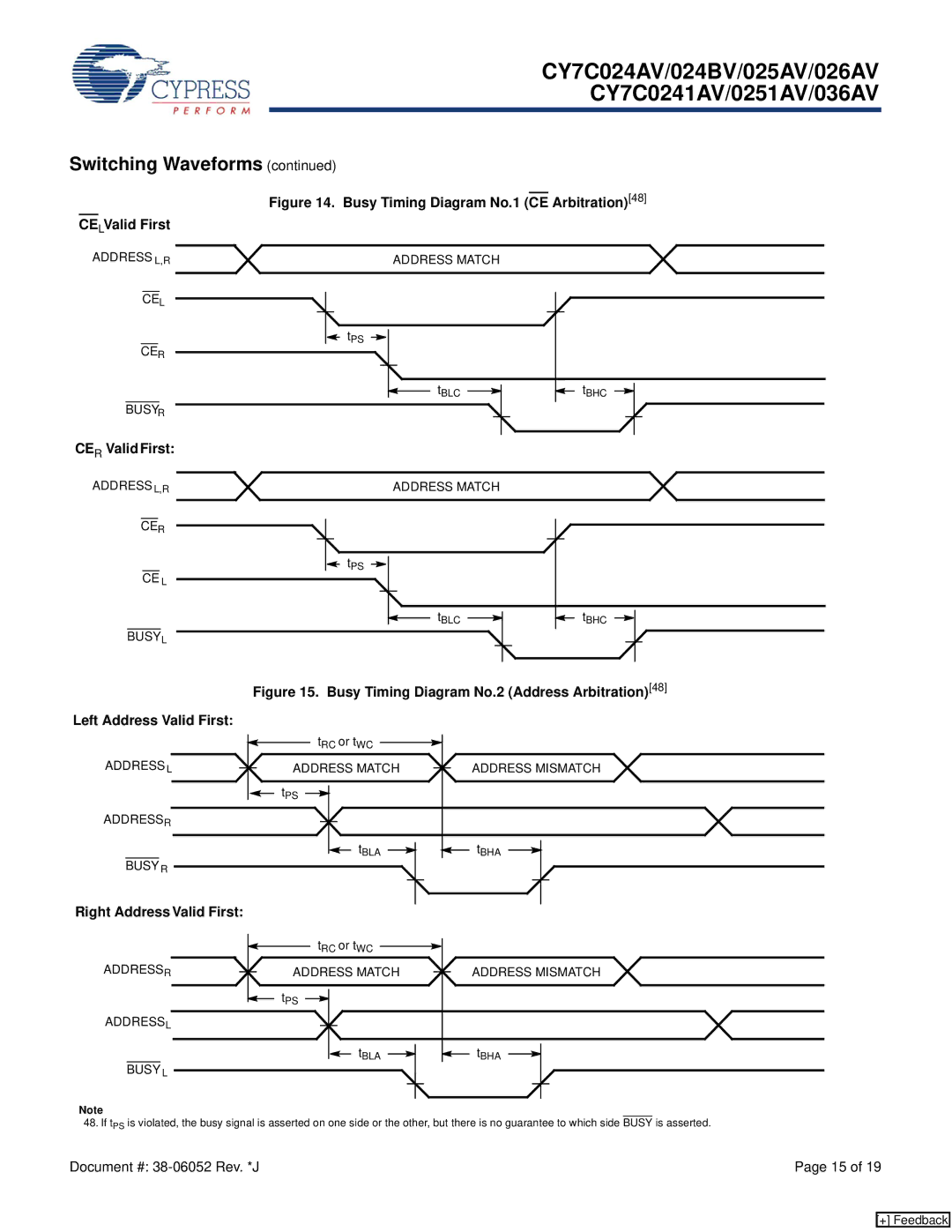

Switching Waveforms (continued)

Figure 14. Busy Timing Diagram No.1 (CE Arbitration)[48]

CELValid First

ADDRESS L,R

CEL

CER

BUSYR

CER ValidFirst:

ADDRESSL,R

CER

CE L

BUSYL

ADDRESS MATCH

tPS

|

|

| tBLC |

|

|

|

|

|

|

| tBHC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADDRESS MATCH |

|

tPS |

|

tBLC | tBHC |

Figure 15. Busy Timing Diagram No.2 (Address Arbitration)[48]

Left Address Valid First:

ADDRESSL

ADDRESSR

BUSY R

tRC or tWC

ADDRESS MATCH |

| ADDRESS MISMATCH |

|

tPS

|

| tBLA |

|

|

|

| tBHA |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

Right Address Valid First:

ADDRESSR

ADDRESSL

BUSY L

tRC or tWC

ADDRESS MATCH |

| ADDRESS MISMATCH |

|

tPS

|

| tBLA |

|

|

|

|

|

|

| tBHA |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note

48. If tPS is violated, the busy signal is asserted on one side or the other, but there is no guarantee to which side BUSY is asserted.

Document #: | Page 15 of 19 |

[+] Feedback