|

| CY7C024AV/024BV/025AV/026AV | |

|

| CY7C0241AV/0251AV/036AV | |

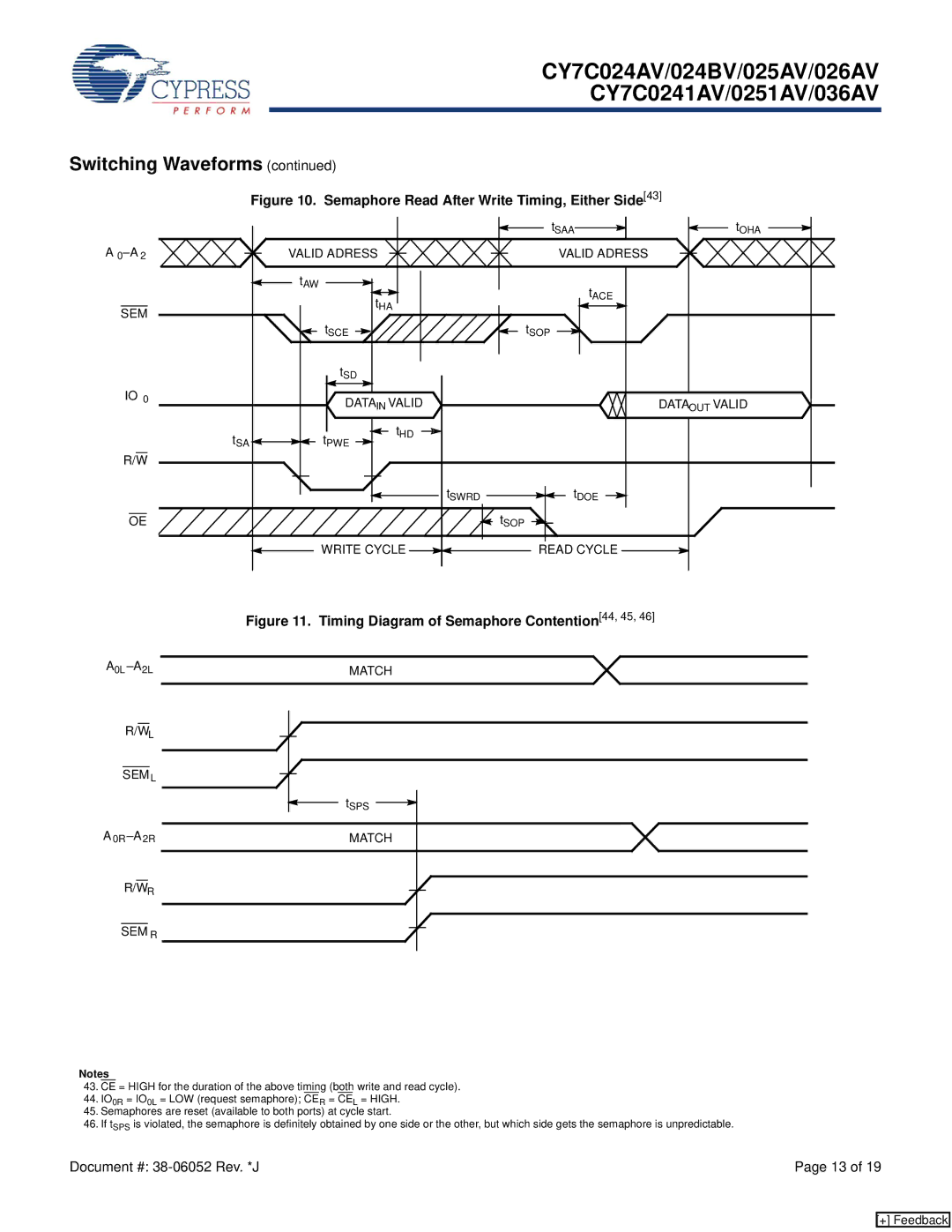

Switching Waveforms (continued) |

|

| |

| Figure 10. Semaphore Read After Write Timing, Either Side[43] | ||

|

| tSAA | tOHA |

A | VALID ADRESS | VALID ADRESS |

|

| tAW | tACE |

|

| tHA |

| |

SEM |

|

| |

tSCE | tSOP |

| |

|

| ||

| tSD |

|

|

IO 0 | DATAIN VALID |

| DATAOUT VALID |

|

| ||

tSA | tHD |

|

|

tPWE |

|

| |

R/W |

|

|

|

| tSWRD | tDOE |

|

OE |

| tSOP |

|

| WRITE CYCLE | READ CYCLE |

|

Figure 11. Timing Diagram of Semaphore Contention[44, 45, 46]

A0L

R/WL

SEML

A

MATCH

tSPS

MATCH

R/WR

SEM R

Notes

43.CE = HIGH for the duration of the above timing (both write and read cycle).

44.IO0R = IO0L = LOW (request semaphore); CER = CEL = HIGH.

45.Semaphores are reset (available to both ports) at cycle start.

46.If tSPS is violated, the semaphore is definitely obtained by one side or the other, but which side gets the semaphore is unpredictable.

Document #: | Page 13 of 19 |

[+] Feedback