CY7C024AV/024BV/025AV/026AV

CY7C0241AV/0251AV/036AV

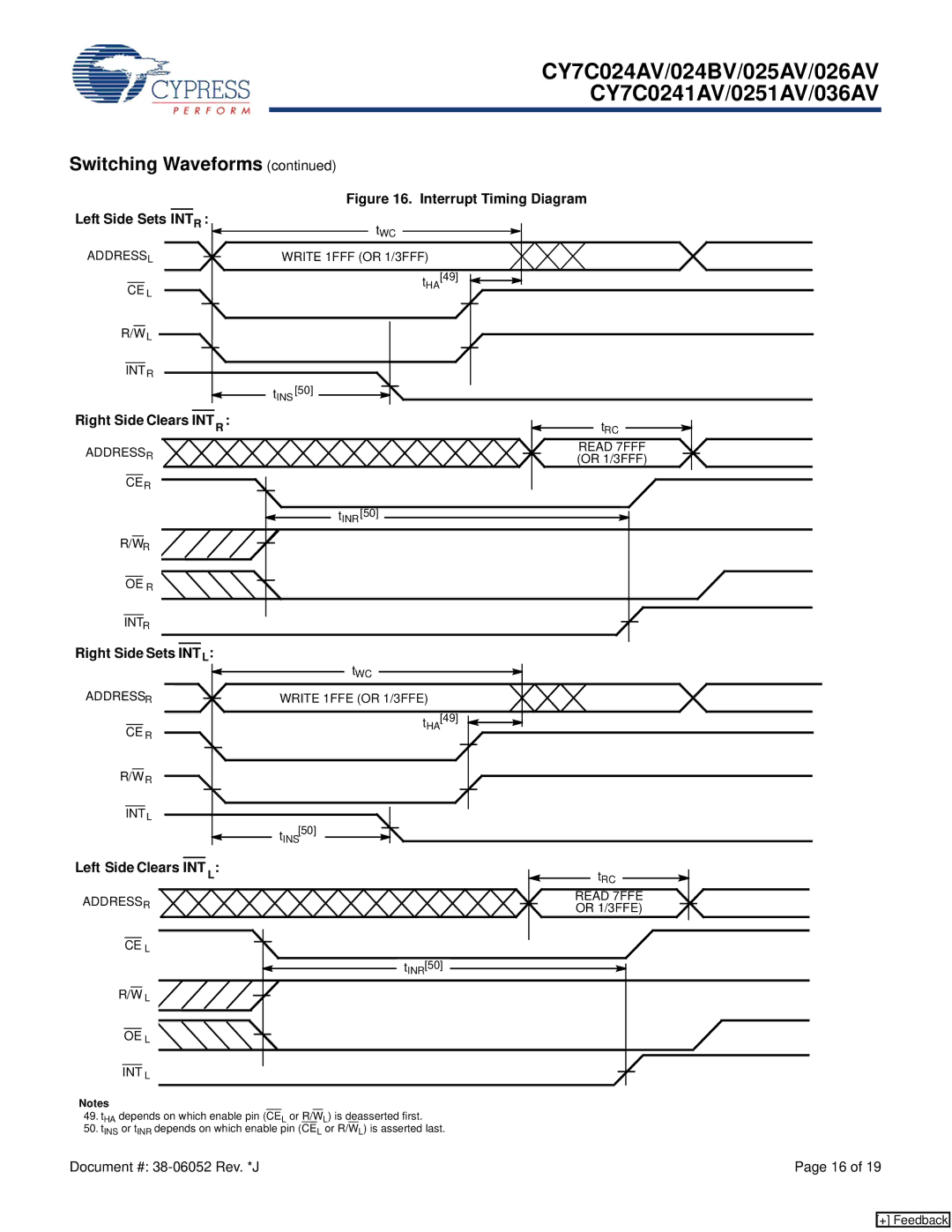

Switching Waveforms (continued)

Figure 16. Interrupt Timing Diagram

Left Side Sets INTR : | tWC |

| |

ADDRESSL | WRITE 1FFF (OR 1/3FFF) |

CE L | tHA[49] |

| |

R/WL |

|

INTR |

|

| tINS [50] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Right Side Clears INTR : |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| t |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

| RC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADDRESSR |

|

|

|

|

| READ 7FFF |

|

|

| ||||||||

|

|

|

|

| (OR 1/3FFF) |

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CER |

tINR[50] |

R/WR |

OE R |

INTR |

Right Side Sets INTL:

ADDRESSR

CE R

R/WR

INTL

tWC |

WRITE 1FFE (OR 1/3FFE) |

tHA[49] |

tINS[50] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Left Side Clears INT L: |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| tRC |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADDRESSR | READ 7FFE |

|

|

| |||||||||||

|

|

|

|

| OR 1/3FFE) |

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CE L |

tINR[50] |

R/W L |

OE L |

INT L |

Notes

49.tHA depends on which enable pin (CEL or R/WL) is deasserted first.

50.tINS or tINR depends on which enable pin (CEL or R/WL) is asserted last.

Document #: | Page 16 of 19 |

[+] Feedback