CY7C1320CV18, CY7C1916CV18, CY7C1316CV18, CY7C1318CV18 specifications

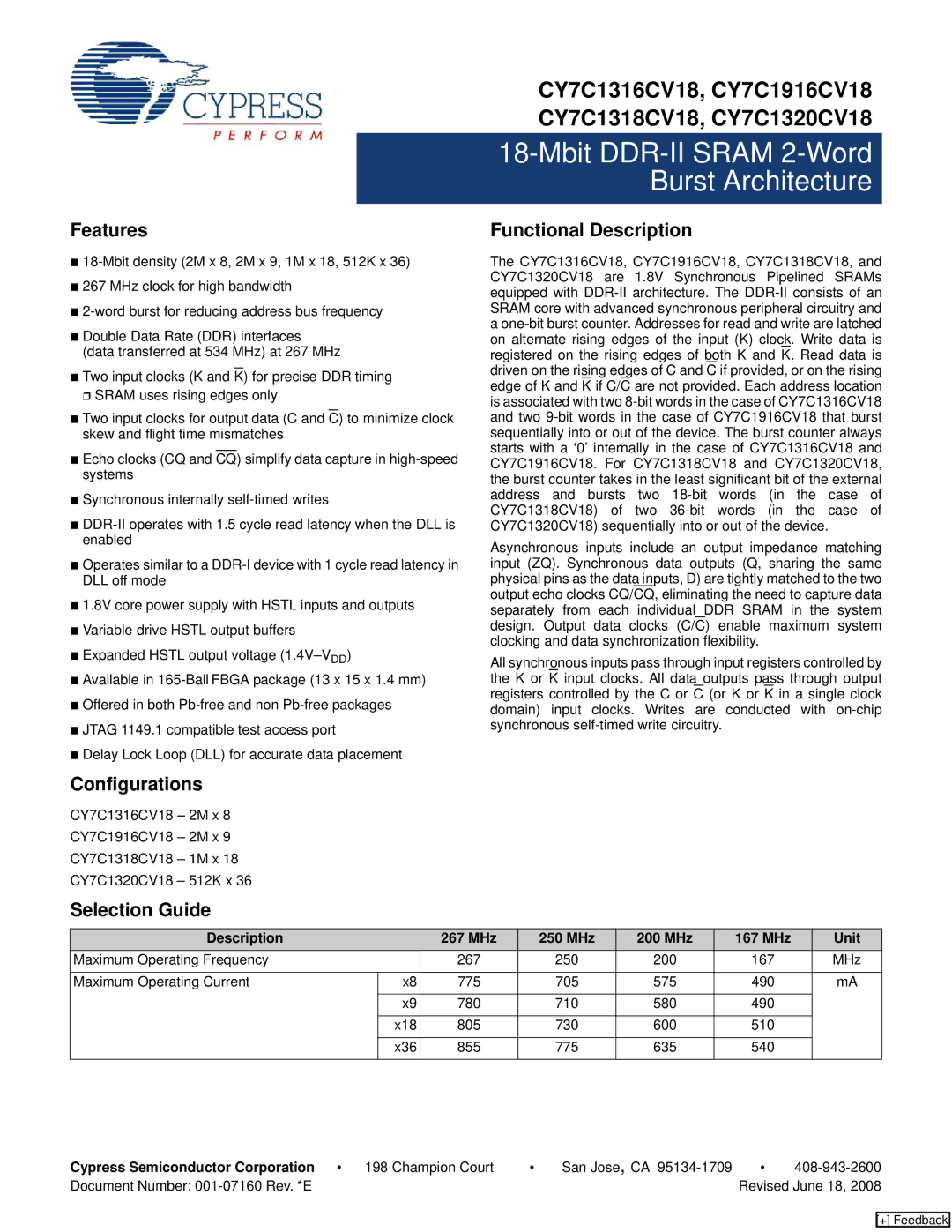

Cypress Semiconductor, a leading provider of high-performance memory solutions, offers a range of Static Random-Access Memory (SRAM) products ideal for various applications. Among these are the CY7C1320CV18, CY7C1916CV18, CY7C1316CV18, and CY7C1318CV18, each designed to meet the demands of modern electronic systems with distinctive features, technologies, and characteristics.The CY7C1320CV18 is a high-performance 2-Mbit SRAM that operates at a voltage of 1.8V. Designed with speed in mind, it has access times as low as 12 ns, making it suitable for applications requiring quick data retrieval. The device features a simple asynchronous interface, allowing it to be easily integrated into various circuits. With a low power consumption profile and the ability to operate under a wide temperature range, the CY7C1320CV18 is an ideal choice for battery-operated devices and industrial environments.

Following closely, the CY7C1916CV18 is a highly integrated, 16-Mbit synchronous SRAM. This device stands out due to its robust data transfer capabilities, supporting a single-cycle read and write operation, which greatly enhances system performance. The device operates with a supply voltage of 1.8V and features an impressive latency, making it perfect for high-speed applications such as digital signal processing and telecommunications. The unique pipelined architecture allows for higher throughput and efficiency in memory access.

The CY7C1316CV18 is another notable member of this family, featuring 16K x 8 bits of memory. It is characterized by low power consumption and a fast access time, which helps to reduce latency in critical applications. With a simple asynchronous interface and competitive pricing, the CY7C1316CV18 is suitable for consumer electronics and automotive applications that require reliable performance.

Lastly, the CY7C1318CV18 is a comprehensive solution featuring 32K x 8 bits of memory. This device also operates with low power and high speed, making it efficient for caching, buffering, and temporary storage applications. Its compatibility with industry standards makes it easily integrable into existing systems.

In summary, the CY7C1320CV18, CY7C1916CV18, CY7C1316CV18, and CY7C1318CV18 SRAM devices from Cypress Semiconductor showcase cutting-edge technology, high performance, and versatility, catering to the evolving needs of today's electronics, from telecommunications to consumer devices. Their low power consumption, high-speed access, and reliable data integrity make them essential components in modern electronic designs.