CY7C1511V18, CY7C1526V18

CY7C1513V18, CY7C1515V18

TAP AC Switching Characteristics

Over the Operating Range [15, 16]

Parameter | Description | Min | Max | Unit |

tTCYC | TCK Clock Cycle Time | 50 |

| ns |

tTF | TCK Clock Frequency |

| 20 | MHz |

tTH | TCK Clock HIGH | 20 |

| ns |

tTL | TCK Clock LOW | 20 |

| ns |

Setup Times |

|

|

|

|

|

|

|

|

|

tTMSS | TMS Setup to TCK Clock Rise | 5 |

| ns |

tTDIS | TDI Setup to TCK Clock Rise | 5 |

| ns |

tCS | Capture Setup to TCK Rise | 5 |

| ns |

Hold Times |

|

|

|

|

tTMSH | TMS Hold after TCK Clock Rise | 5 |

| ns |

tTDIH | TDI Hold after Clock Rise | 5 |

| ns |

tCH | Capture Hold after Clock Rise | 5 |

| ns |

Output Times |

|

|

|

|

|

|

|

|

|

tTDOV | TCK Clock LOW to TDO Valid |

| 10 | ns |

tTDOX | TCK Clock LOW to TDO Invalid | 0 |

| ns |

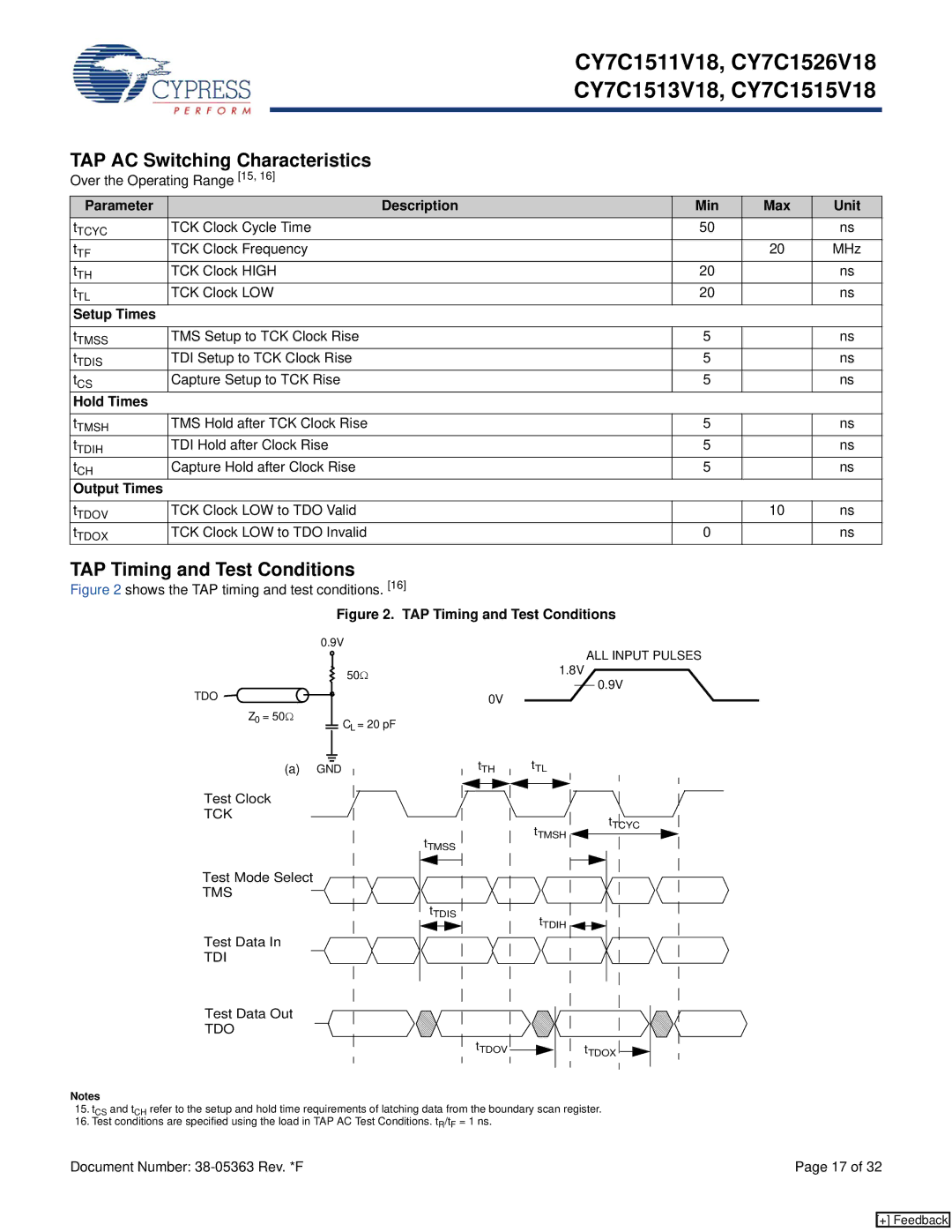

TAP Timing and Test Conditions

Figure 2 shows the TAP timing and test conditions. [16]

Figure 2. TAP Timing and Test Conditions

|

|

| 0.9V | |||

|

|

|

|

|

| 50Ω |

|

|

|

|

|

| |

|

|

|

|

|

| |

TDO |

|

|

|

|

|

|

Z0 | = 50Ω |

|

|

| CL = 20 pF | |

|

|

| ||||

|

|

|

| |||

|

|

|

|

|

| |

|

|

|

|

|

| |

|

|

|

|

|

|

|

ALL INPUT PULSES

1.8V

0.9V

0V

(a)GND

Test Clock

TCK

Test Mode Select

TMS

Test Data In

TDI

Test Data Out

TDO

tTH

tTMSS

tTDIS

tTL

tTCYC

tTMSH ![]()

tTDIH ![]()

![]()

tTDOV |

|

|

| t |

|

|

| ||

| ||||

|

|

|

| TDOX |

Notes

15.tCS and tCH refer to the setup and hold time requirements of latching data from the boundary scan register.

16.Test conditions are specified using the load in TAP AC Test Conditions. tR/tF = 1 ns.

Document Number: | Page 17 of 32 |

[+] Feedback