CY8C24223A, CY8C24423A

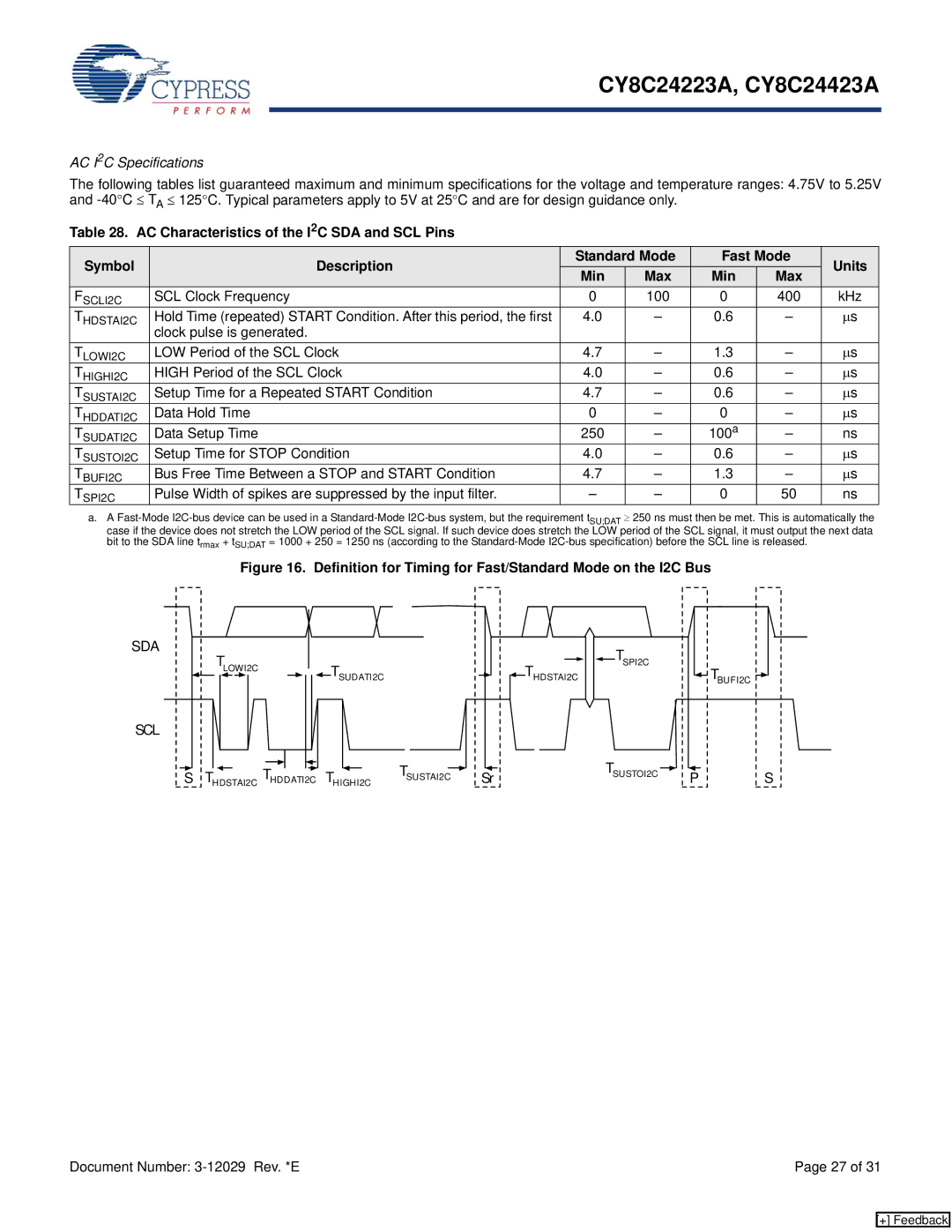

AC I2C Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and

Table 28. AC Characteristics of the I2C SDA and SCL Pins

Symbol | Description | Standard Mode | Fast Mode | Units | |||

Min | Max | Min | Max | ||||

|

|

| |||||

FSCLI2C | SCL Clock Frequency | 0 | 100 | 0 | 400 | kHz | |

THDSTAI2C | Hold Time (repeated) START Condition. After this period, the first | 4.0 | – | 0.6 | – | μs | |

| clock pulse is generated. |

|

|

|

|

| |

TLOWI2C | LOW Period of the SCL Clock | 4.7 | – | 1.3 | – | μs | |

THIGHI2C | HIGH Period of the SCL Clock | 4.0 | – | 0.6 | – | μs | |

TSUSTAI2C | Setup Time for a Repeated START Condition | 4.7 | – | 0.6 | – | μs | |

THDDATI2C | Data Hold Time | 0 | – | 0 | – | μs | |

TSUDATI2C | Data Setup Time | 250 | – | 100a | – | ns | |

TSUSTOI2C | Setup Time for STOP Condition | 4.0 | – | 0.6 | – | μs | |

TBUFI2C | Bus Free Time Between a STOP and START Condition | 4.7 | – | 1.3 | – | μs | |

TSPI2C | Pulse Width of spikes are suppressed by the input filter. | – | – | 0 | 50 | ns | |

a.A

Figure 16. Definition for Timing for Fast/Standard Mode on the I2C Bus

SDA | TLOWI2C |

|

|

| TSUDATI2C |

| |

|

|

| |

SCL |

|

|

|

S | THDSTAI2C THDDATI2C | THIGHI2C | TSUSTAI2C |

![]()

![]() THDSTAI2C

THDSTAI2C

![]() Sr

Sr

TSPI2C |

| TBUFI2C |

|

| |

TSUSTOI2C | P | S |

|

Document Number: | Page 27 of 31 |

[+] Feedback