Table 3: Bus throughput from the Hitachi Node Controller

Bus | Throughput |

|

|

Connection between nodes | 400 MHz FSB = 4.8 GB/sec. |

| 667 MHz FSB = 5.3 GB/sec. |

|

|

Baseboard Management Controller

The Baseboard Management Controller (BMC) is the main controller for Intelligent Platform Management Interface (IPMI), a common interface to hardware and firmware used to monitor system health and manage the system. The BMC manages the interface between system management software and the hardware in the server blade. It is connected to the service processor (SVP) inside the Switch & Management Module. The BMC and SVP cooperate with each other to control and monitor the entire system. Sensors built into the system report to the BMC on different parameters such as temperature, cooling fan speeds, power, mode, OS status, etc. The BMC can send alerts to the system administrator if the parameters vary from specified preset limits, indicating a potential failure of a component or the system.

Memory System

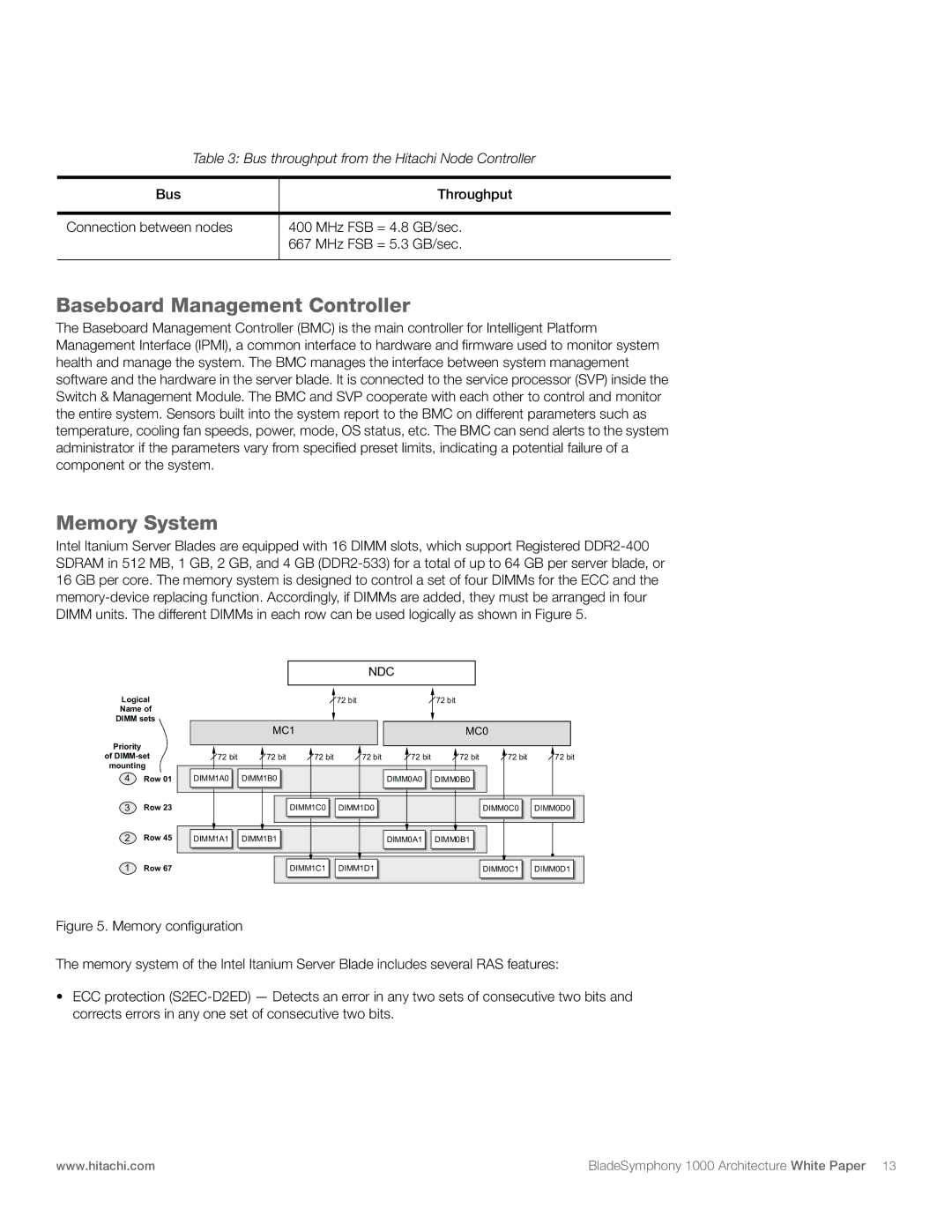

Intel Itanium Server Blades are equipped with 16 DIMM slots, which support Registered

NDC

Logical

Name of

DIMM sets

Priority

of

mounting

4Row 01

3Row 23

2Row 45

1Row 67

| 72 bit |

|

| 72 bit |

|

|

|

|

|

|

|

|

|

|

MC11 |

|

| MC00 | |

|

|

|

|

|

72 bit | 72 bit | 72 bit | 72 bit | 72 bit | 72 bit | 72 bit | 72 bit |

DIMM1A0 | DIMM1B0 |

|

| DIMM0A0 | DIMM0B0 |

|

|

DIMM1C0 | DIMM1D0 | DIMM0C0 | DIMM0D0 |

DIMM1A1 | DIMM1B1 | DIMM0A1 | DIMM0B1 |

DIMM1C1 | DIMM1D1 | DIMM0C1 | DIMM0D1 |

Figure 5. Memory configuration

The memory system of the Intel Itanium Server Blade includes several RAS features:

•ECC protection (S2EC-D2ED) — Detects an error in any two sets of consecutive two bits and corrects errors in any one set of consecutive two bits.

www.hitachi.com | BladeSymphony 1000 Architecture White Paper 13 |