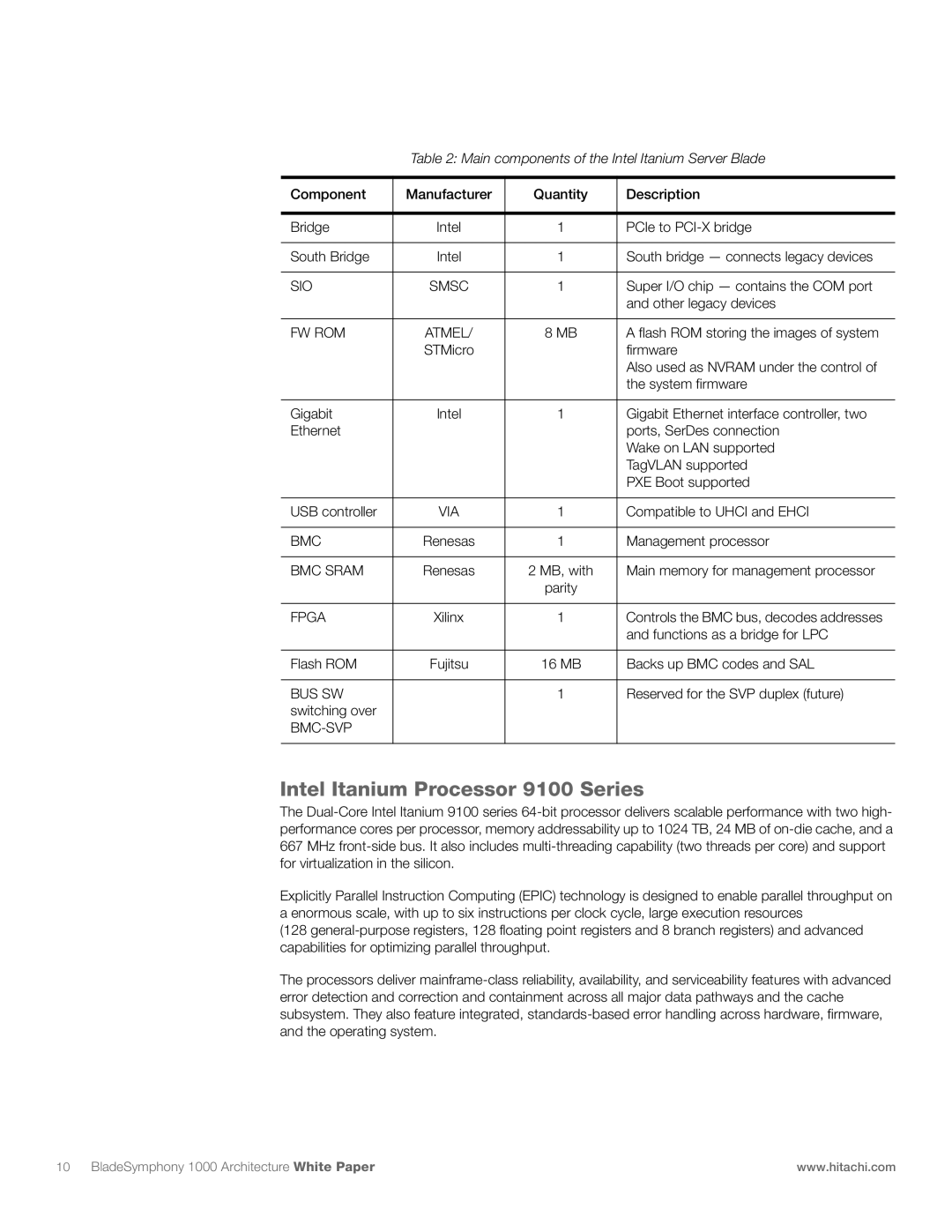

Table 2: Main components of the Intel Itanium Server Blade

Component | Manufacturer | Quantity | Description |

|

|

|

|

Bridge | Intel | 1 | PCIe to |

|

|

|

|

South Bridge | Intel | 1 | South bridge — connects legacy devices |

|

|

|

|

SIO | SMSC | 1 | Super I/O chip — contains the COM port |

|

|

| and other legacy devices |

|

|

|

|

FW ROM | ATMEL/ | 8 MB | A flash ROM storing the images of system |

| STMicro |

| firmware |

|

|

| Also used as NVRAM under the control of |

|

|

| the system firmware |

|

|

|

|

Gigabit | Intel | 1 | Gigabit Ethernet interface controller, two |

Ethernet |

|

| ports, SerDes connection |

|

|

| Wake on LAN supported |

|

|

| TagVLAN supported |

|

|

| PXE Boot supported |

|

|

|

|

USB controller | VIA | 1 | Compatible to UHCI and EHCI |

|

|

|

|

BMC | Renesas | 1 | Management processor |

|

|

|

|

BMC SRAM | Renesas | 2 MB, with | Main memory for management processor |

|

| parity |

|

|

|

|

|

FPGA | Xilinx | 1 | Controls the BMC bus, decodes addresses |

|

|

| and functions as a bridge for LPC |

|

|

|

|

Flash ROM | Fujitsu | 16 MB | Backs up BMC codes and SAL |

|

|

|

|

BUS SW |

| 1 | Reserved for the SVP duplex (future) |

switching over |

|

|

|

|

|

| |

|

|

|

|

Intel Itanium Processor 9100 Series

The

Explicitly Parallel Instruction Computing (EPIC) technology is designed to enable parallel throughput on a enormous scale, with up to six instructions per clock cycle, large execution resources

(128

The processors deliver

10 BladeSymphony 1000 Architecture White Paper | www.hitachi.com |