BIOS |

|

|

|

|

|

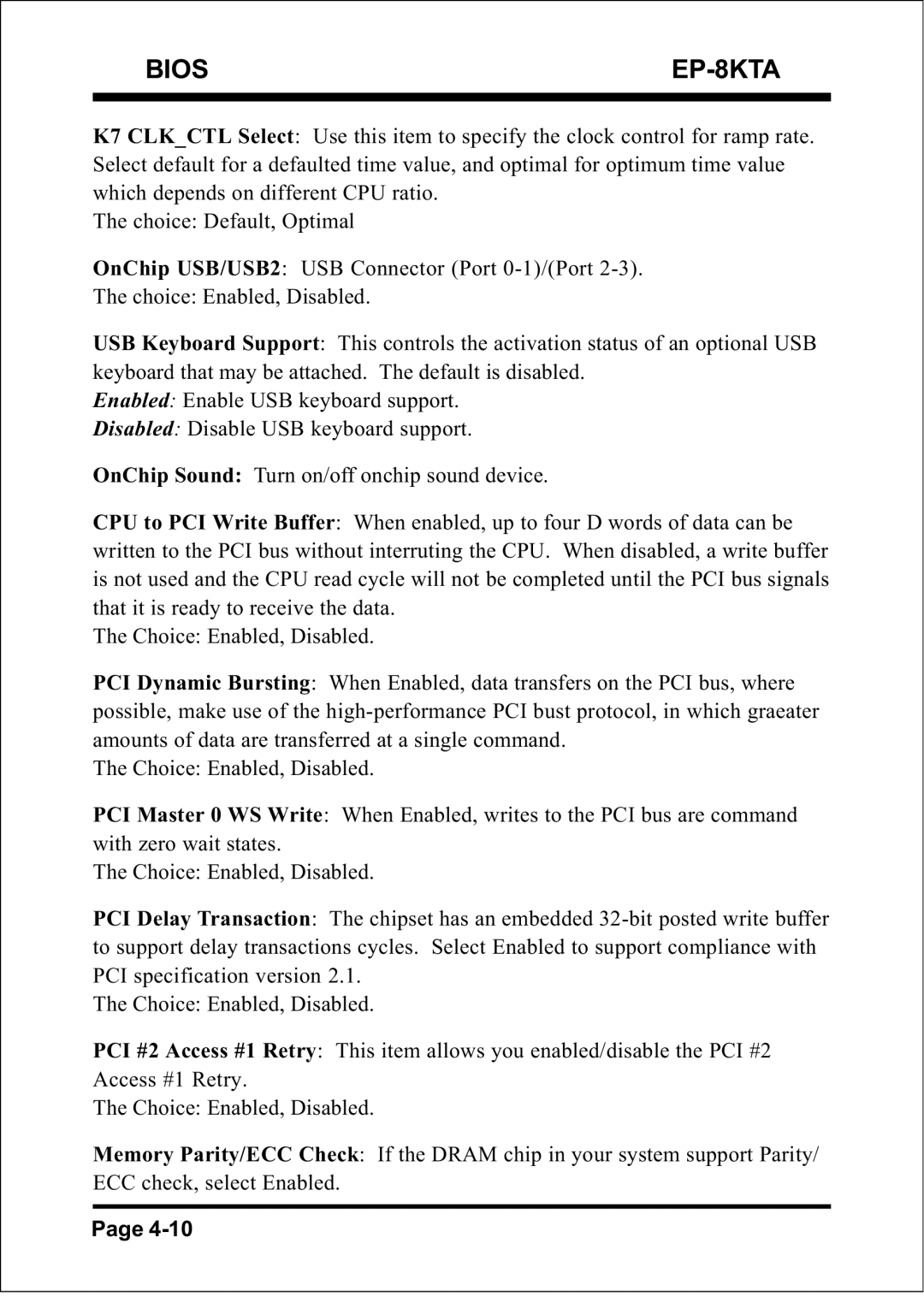

K7 CLK_CTL Select: Use this item to specify the clock control for ramp rate. Select default for a defaulted time value, and optimal for optimum time value which depends on different CPU ratio.

The choice: Default, Optimal

OnChip USB/USB2: USB Connector (Port

The choice: Enabled, Disabled.

USB Keyboard Support: This controls the activation status of an optional USB keyboard that may be attached. The default is disabled.

Enabled: Enable USB keyboard support.

Disabled: Disable USB keyboard support.

OnChip Sound: Turn on/off onchip sound device.

CPU to PCI Write Buffer: When enabled, up to four D words of data can be written to the PCI bus without interruting the CPU. When disabled, a write buffer is not used and the CPU read cycle will not be completed until the PCI bus signals that it is ready to receive the data.

The Choice: Enabled, Disabled.

PCI Dynamic Bursting: When Enabled, data transfers on the PCI bus, where possible, make use of the

The Choice: Enabled, Disabled.

PCI Master 0 WS Write: When Enabled, writes to the PCI bus are command with zero wait states.

The Choice: Enabled, Disabled.

PCI Delay Transaction: The chipset has an embedded

The Choice: Enabled, Disabled.

PCI #2 Access #1 Retry: This item allows you enabled/disable the PCI #2 Access #1 Retry.

The Choice: Enabled, Disabled.

Memory Parity/ECC Check: If the DRAM chip in your system support Parity/ ECC check, select Enabled.

Page