Intel® 80219 General Purpose PCI Processor

Summary Table of Changes

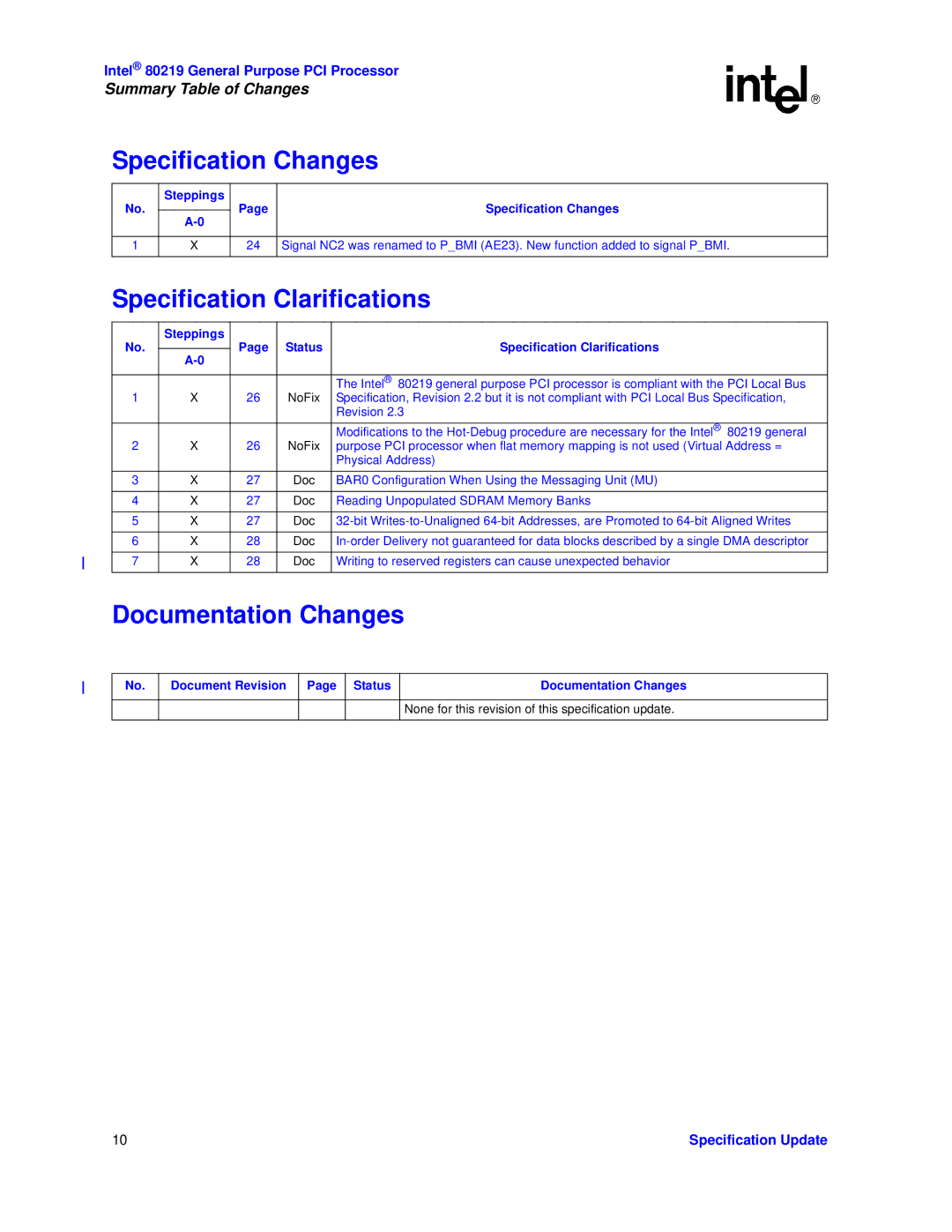

Specification Changes

No. | Steppings | Page | Specification Changes | |

| ||||

|

|

| ||

|

|

|

| |

1 | X | 24 | Signal NC2 was renamed to P_BMI (AE23). New function added to signal P_BMI. | |

|

|

|

|

Specification Clarifications

No. | Steppings | Page | Status | Specification Clarifications | |

| |||||

|

|

|

| ||

|

|

|

|

| |

|

|

|

| The Intel® 80219 general purpose PCI processor is compliant with the PCI Local Bus | |

1 | X | 26 | NoFix | Specification, Revision 2.2 but it is not compliant with PCI Local Bus Specification, | |

|

|

|

| Revision 2.3 | |

|

|

|

| Modifications to the | |

2 | X | 26 | NoFix | purpose PCI processor when flat memory mapping is not used (Virtual Address = | |

|

|

|

| Physical Address) | |

|

|

|

|

| |

3 | X | 27 | Doc | BAR0 Configuration When Using the Messaging Unit (MU) | |

|

|

|

|

| |

4 | X | 27 | Doc | Reading Unpopulated SDRAM Memory Banks | |

|

|

|

|

| |

5 | X | 27 | Doc | ||

|

|

|

|

| |

6 | X | 28 | Doc | ||

|

|

|

|

| |

7 | X | 28 | Doc | Writing to reserved registers can cause unexpected behavior | |

|

|

|

|

|

Documentation Changes

No. | Document Revision Page Status | Documentation Changes |

None for this revision of this specification update.

10 | Specification Update |