Intel® 80219 General Purpose PCI Processor

Summary Table of Changes

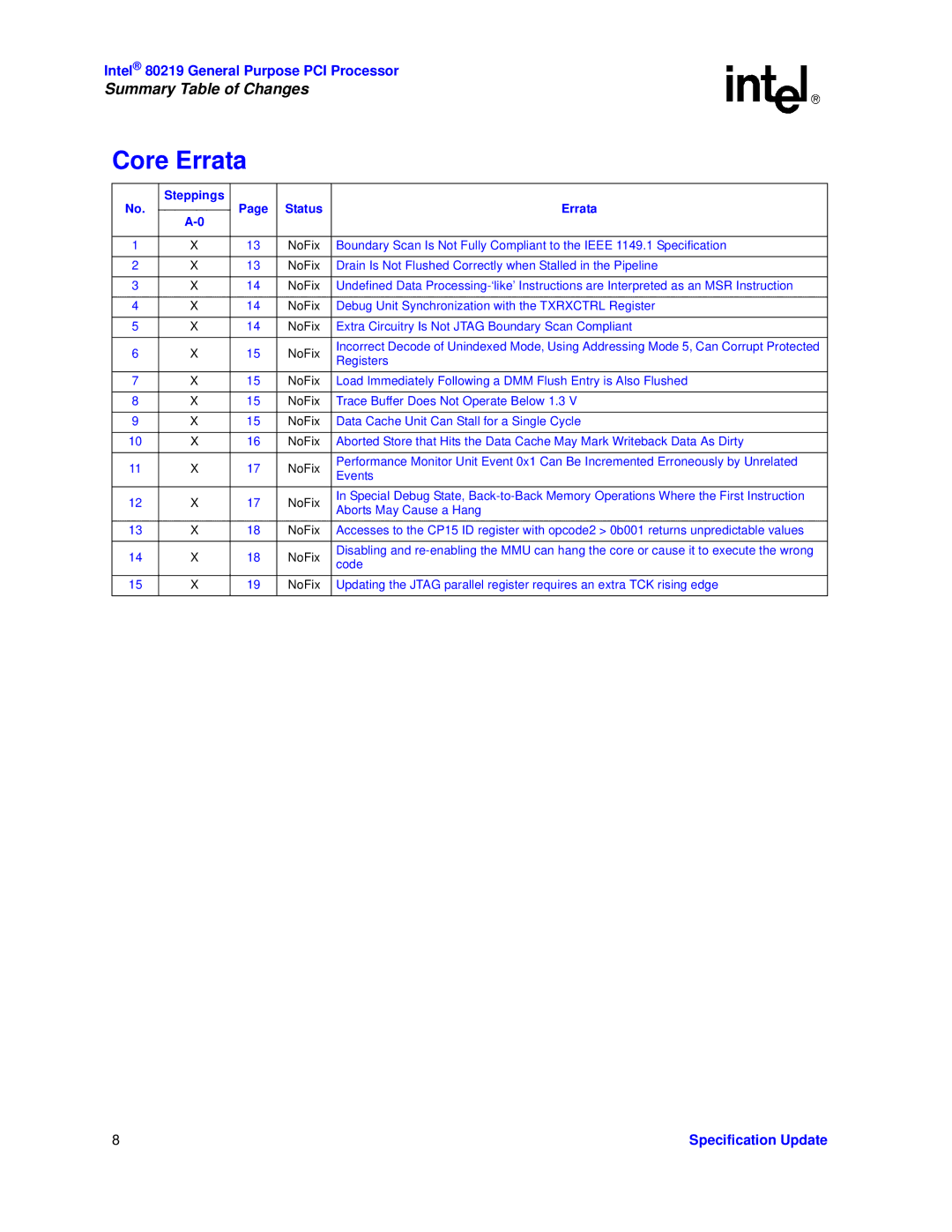

Core Errata

No. | Steppings | Page | Status | Errata | |

| |||||

|

|

|

| ||

|

|

|

|

| |

1 | X | 13 | NoFix | Boundary Scan Is Not Fully Compliant to the IEEE 1149.1 Specification | |

|

|

|

|

| |

2 | X | 13 | NoFix | Drain Is Not Flushed Correctly when Stalled in the Pipeline | |

|

|

|

|

| |

3 | X | 14 | NoFix | Undefined Data | |

|

|

|

|

| |

4 | X | 14 | NoFix | Debug Unit Synchronization with the TXRXCTRL Register | |

|

|

|

|

| |

5 | X | 14 | NoFix | Extra Circuitry Is Not JTAG Boundary Scan Compliant | |

|

|

|

|

| |

6 | X | 15 | NoFix | Incorrect Decode of Unindexed Mode, Using Addressing Mode 5, Can Corrupt Protected | |

Registers | |||||

|

|

|

| ||

7 | X | 15 | NoFix | Load Immediately Following a DMM Flush Entry is Also Flushed | |

|

|

|

|

| |

8 | X | 15 | NoFix | Trace Buffer Does Not Operate Below 1.3 V | |

|

|

|

|

| |

9 | X | 15 | NoFix | Data Cache Unit Can Stall for a Single Cycle | |

|

|

|

|

| |

10 | X | 16 | NoFix | Aborted Store that Hits the Data Cache May Mark Writeback Data As Dirty | |

|

|

|

|

| |

11 | X | 17 | NoFix | Performance Monitor Unit Event 0x1 Can Be Incremented Erroneously by Unrelated | |

Events | |||||

|

|

|

| ||

|

|

|

|

| |

12 | X | 17 | NoFix | In Special Debug State, | |

Aborts May Cause a Hang | |||||

|

|

|

| ||

13 | X | 18 | NoFix | Accesses to the CP15 ID register with opcode2 > 0b001 returns unpredictable values | |

|

|

|

|

| |

14 | X | 18 | NoFix | Disabling and | |

code | |||||

|

|

|

| ||

|

|

|

|

| |

15 | X | 19 | NoFix | Updating the JTAG parallel register requires an extra TCK rising edge | |

|

|

|

|

|

8 | Specification Update |