|

|

|

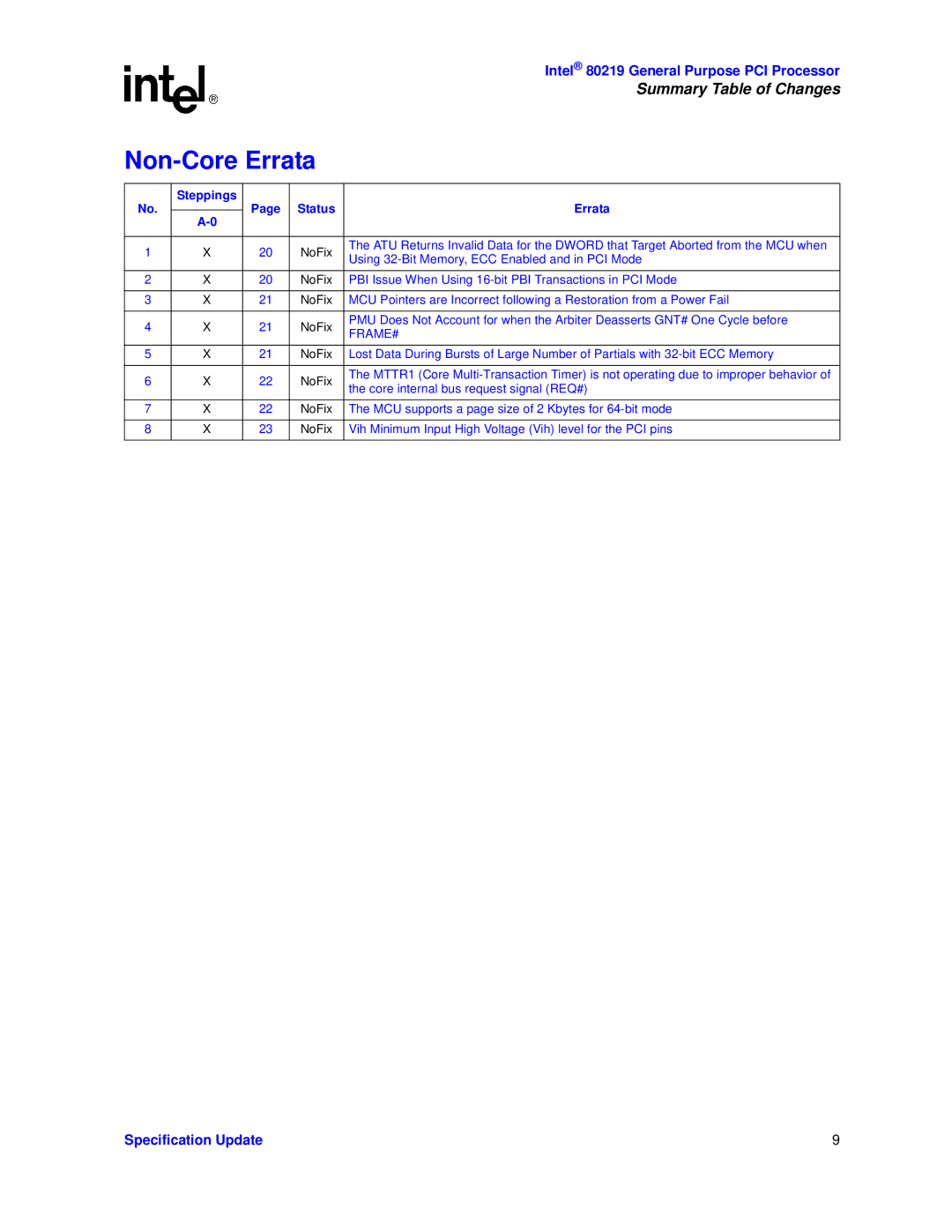

| Intel® 80219 General Purpose PCI Processor | |

|

|

|

| Summary Table of Changes | |

|

| ||||

|

|

|

|

| |

No. | Steppings | Page | Status | Errata | |

| |||||

|

|

|

| ||

|

|

|

|

| |

1 | X | 20 | NoFix | The ATU Returns Invalid Data for the DWORD that Target Aborted from the MCU when | |

Using | |||||

|

|

|

| ||

|

|

|

|

| |

2 | X | 20 | NoFix | PBI Issue When Using | |

|

|

|

|

| |

3 | X | 21 | NoFix | MCU Pointers are Incorrect following a Restoration from a Power Fail | |

|

|

|

|

| |

4 | X | 21 | NoFix | PMU Does Not Account for when the Arbiter Deasserts GNT# One Cycle before | |

FRAME# | |||||

|

|

|

| ||

|

|

|

|

| |

5 | X | 21 | NoFix | Lost Data During Bursts of Large Number of Partials with | |

|

|

|

|

| |

6 | X | 22 | NoFix | The MTTR1 (Core | |

the core internal bus request signal (REQ#) | |||||

|

|

|

| ||

7 | X | 22 | NoFix | The MCU supports a page size of 2 Kbytes for | |

|

|

|

|

| |

8 | X | 23 | NoFix | Vih Minimum Input High Voltage (Vih) level for the PCI pins | |

|

|

|

|

| |

Specification Update | 9 |