Intel® 80219 General Purpose PCI Processor

Core Errata

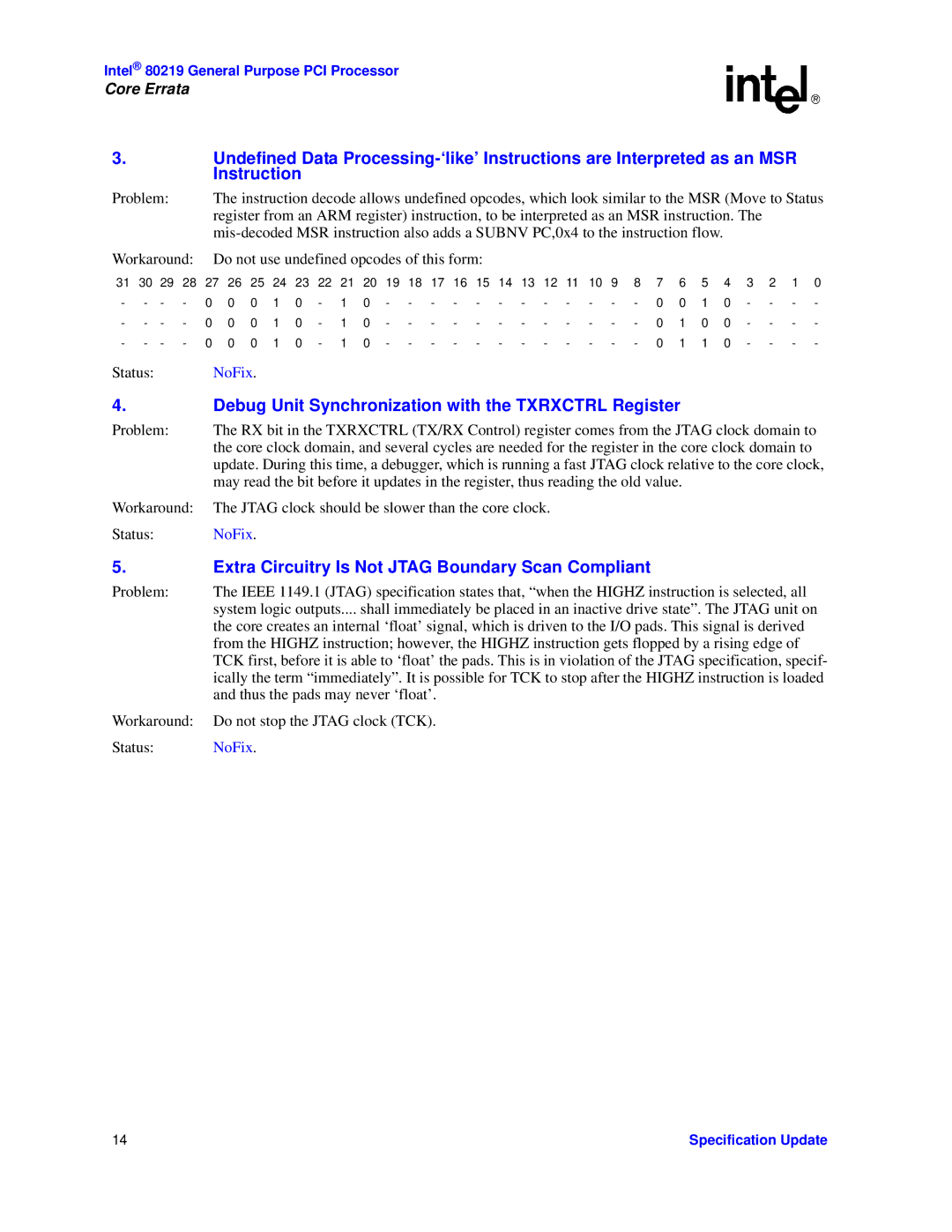

3.Undefined Data

Problem: |

| The instruction decode allows undefined opcodes, which look similar to the MSR (Move to Status | |||||||||||||||||||||||||||||

|

|

|

| register from an ARM register) instruction, to be interpreted as an MSR instruction. The |

|

|

| ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

Workaround: | Do not use undefined opcodes of this form: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

- | - | - | - | 0 | 0 | 0 | 1 | 0 | - | 1 | 0 | - | - | - | - | - | - | - | - | - | - | - | - | 0 | 0 | 1 | 0 | - | - | - | - |

- | - | - | - | 0 | 0 | 0 | 1 | 0 | - | 1 | 0 | - | - | - | - | - | - | - | - | - | - | - | - | 0 | 1 | 0 | 0 | - | - | - | - |

- | - | - | - | 0 | 0 | 0 | 1 | 0 | - | 1 | 0 | - | - | - | - | - | - | - | - | - | - | - | - | 0 | 1 | 1 | 0 | - | - | - | - |

Status: NoFix.

4.Debug Unit Synchronization with the TXRXCTRL Register

Problem: | The RX bit in the TXRXCTRL (TX/RX Control) register comes from the JTAG clock domain to |

| the core clock domain, and several cycles are needed for the register in the core clock domain to |

| update. During this time, a debugger, which is running a fast JTAG clock relative to the core clock, |

| may read the bit before it updates in the register, thus reading the old value. |

Workaround: | The JTAG clock should be slower than the core clock. |

Status: | NoFix. |

5.Extra Circuitry Is Not JTAG Boundary Scan Compliant

Problem: | The IEEE 1149.1 (JTAG) specification states that, “when the HIGHZ instruction is selected, all |

| system logic outputs.... shall immediately be placed in an inactive drive state”. The JTAG unit on |

| the core creates an internal ‘float’ signal, which is driven to the I/O pads. This signal is derived |

| from the HIGHZ instruction; however, the HIGHZ instruction gets flopped by a rising edge of |

| TCK first, before it is able to ‘float’ the pads. This is in violation of the JTAG specification, specif- |

| ically the term “immediately”. It is possible for TCK to stop after the HIGHZ instruction is loaded |

| and thus the pads may never ‘float’. |

Workaround: | Do not stop the JTAG clock (TCK). |

Status: | NoFix. |

14 | Specification Update |