ATX12V Power Supply Design Guide

Version 2.0

3.3.1. PWR_OK

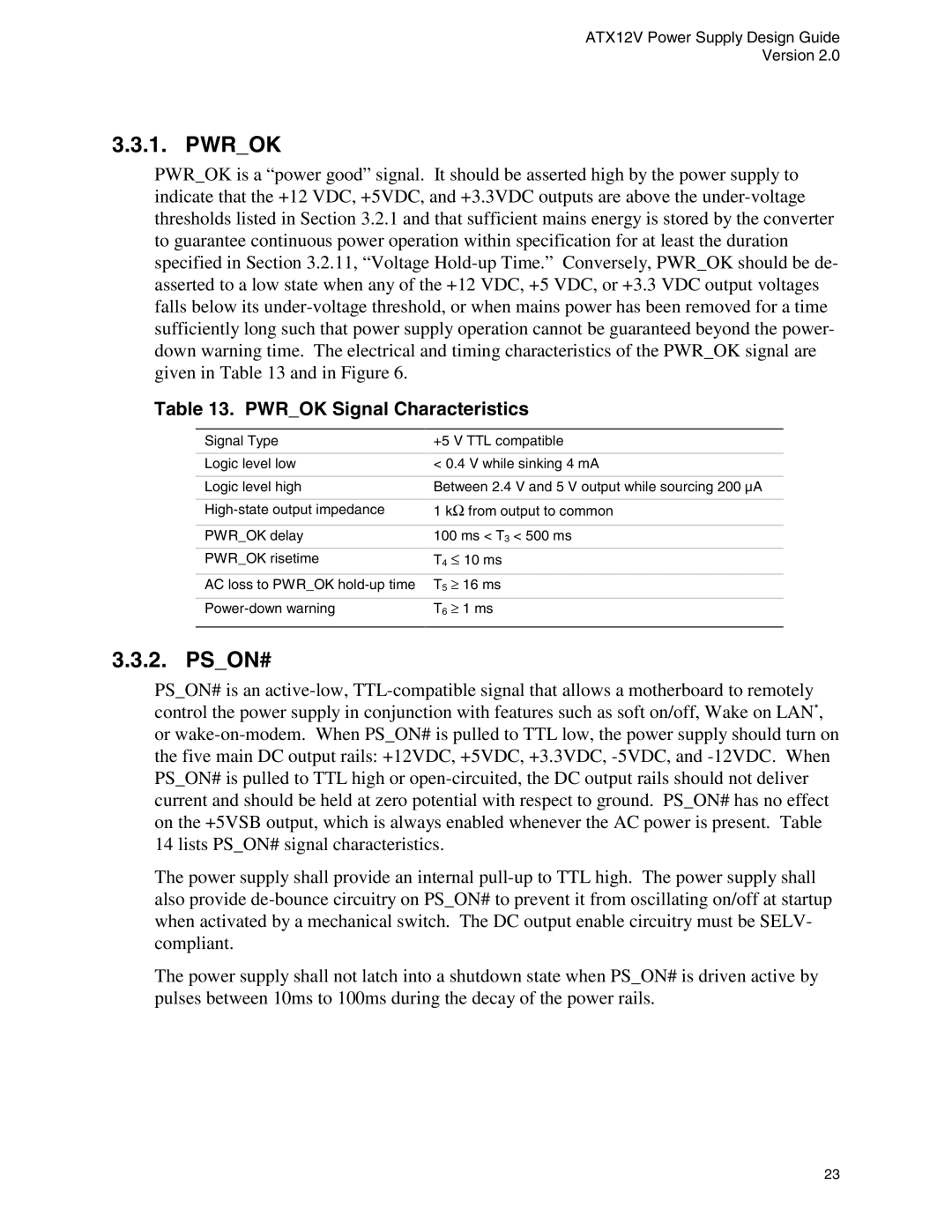

PWR_OK is a “power good” signal. It should be asserted high by the power supply to indicate that the +12 VDC, +5VDC, and +3.3VDC outputs are above the under-voltage thresholds listed in Section 3.2.1 and that sufficient mains energy is stored by the converter to guarantee continuous power operation within specification for at least the duration specified in Section 3.2.11, “Voltage Hold-up Time.” Conversely, PWR_OK should be de- asserted to a low state when any of the +12 VDC, +5 VDC, or +3.3 VDC output voltages falls below its under-voltage threshold, or when mains power has been removed for a time sufficiently long such that power supply operation cannot be guaranteed beyond the power- down warning time. The electrical and timing characteristics of the PWR_OK signal are given in Table 13 and in Figure 6.

Table 13. PWR_OK Signal Characteristics

Signal Type

Logic level low

Logic level high

High-state output impedance

PWR_OK delay

PWR_OK risetime

AC loss to PWR_OK hold-up time

Power-down warning

+5 V TTL compatible

< 0.4 V while sinking 4 mA

Between 2.4 V and 5 V output while sourcing 200 µA

1 kΩ from output to common

100 ms < T3 < 500 ms

T4 ≤ 10 ms

T5 ≥ 16 ms

T6 ≥ 1 ms

3.3.2. PS_ON#

PS_ON# is an active-low, TTL-compatible signal that allows a motherboard to remotely control the power supply in conjunction with features such as soft on/off, Wake on LAN*, or wake-on-modem. When PS_ON# is pulled to TTL low, the power supply should turn on the five main DC output rails: +12VDC, +5VDC, +3.3VDC, -5VDC, and -12VDC. When PS_ON# is pulled to TTL high or open-circuited, the DC output rails should not deliver current and should be held at zero potential with respect to ground. PS_ON# has no effect on the +5VSB output, which is always enabled whenever the AC power is present. Table 14 lists PS_ON# signal characteristics.

The power supply shall provide an internal pull-up to TTL high. The power supply shall also provide de-bounce circuitry on PS_ON# to prevent it from oscillating on/off at startup when activated by a mechanical switch. The DC output enable circuitry must be SELV- compliant.

The power supply shall not latch into a shutdown state when PS_ON# is driven active by pulses between 10ms to 100ms during the decay of the power rails.