Version 1.0, 4/10/02

SDRAM Capacity

The IXM1240 Network Processor Base Card comes with 128MB of SDRAM. The project is configured to use less than 64MB: 32MB of Packet Data Buffers, 16MB for VxWorks, and the balance for IP Route Table Entries. This leaves over 50% available.

The IP Route Table Entries live at 0x8100, simply because they do so by default in all the example designs.

Associated with each of the 16K Buffer Descriptors in SRAM is a 2KB Data Buffer in SDRAM, for a total of 32MB of Data Buffers in SDRAM.

Note that the Data Buffers span the multiple SDRAM bank selects as described in the IXP1200 Hardware Reference Manual. Further, the descriptor freelist is “mixed” at initialization time to give the SDRAM controller the opportunity to access addresses from the multiple DRAM banks. See the appendix (“Buffer Allocation in DRAM”) for more information on “mixing” the freelist.

VxWorks consumes the top 16MB of DRAM.

SRAM and SDRAM Bandwidth

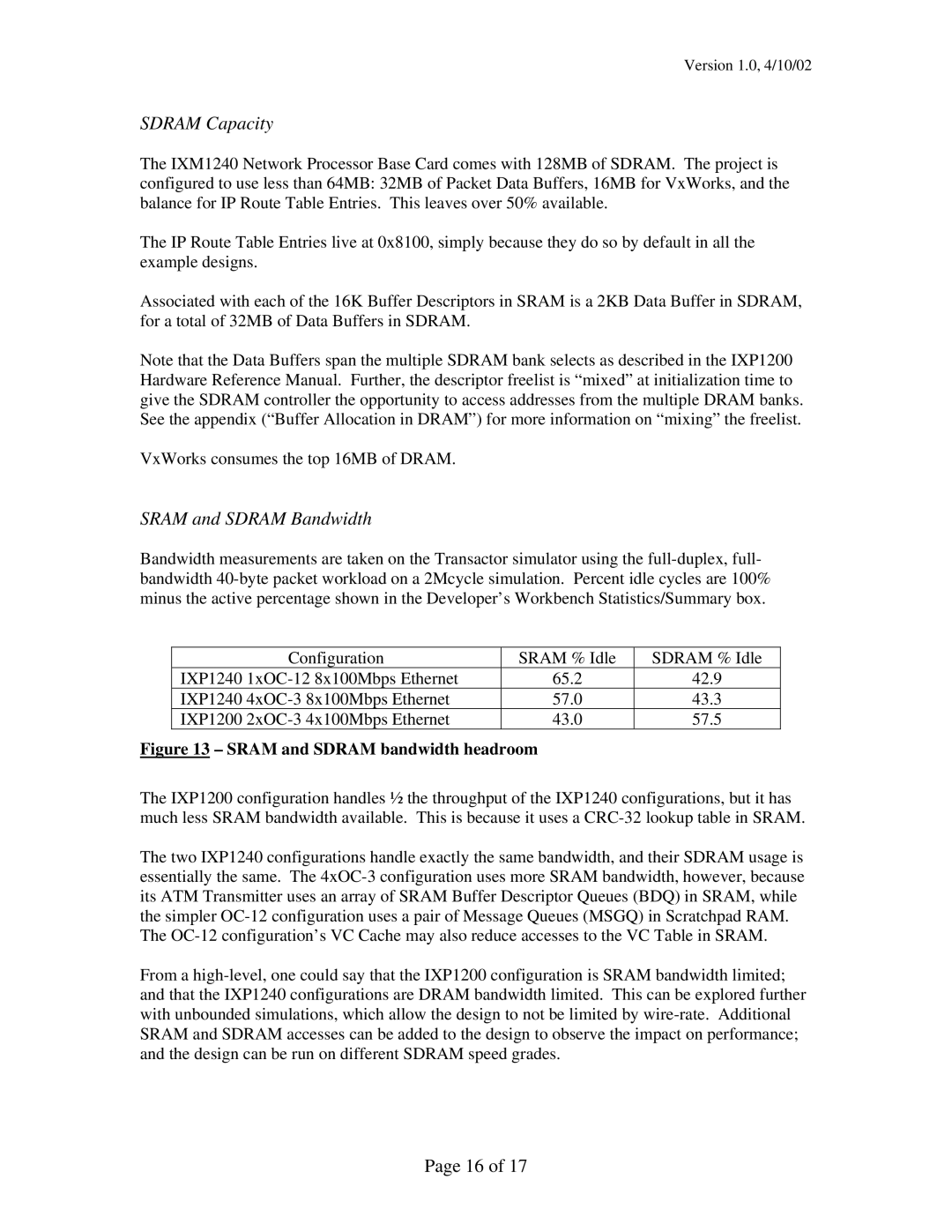

Bandwidth measurements are taken on the Transactor simulator using the

Configuration | SRAM % Idle | SDRAM % Idle |

IXP1240 | 65.2 | 42.9 |

IXP1240 | 57.0 | 43.3 |

IXP1200 | 43.0 | 57.5 |

Figure 13 – SRAM and SDRAM bandwidth headroom

The IXP1200 configuration handles ½ the throughput of the IXP1240 configurations, but it has much less SRAM bandwidth available. This is because it uses a

The two IXP1240 configurations handle exactly the same bandwidth, and their SDRAM usage is essentially the same. The

The

From a

Page 16 of 17