Version 1.0, 4/10/02

IXP12xx ATM OC12/Ethernet IP Router Example Design

Performance and Headroom Analysis

OVERVIEW

This documents details the performance and headroom analysis done on the IXP12xx ATM OC12 / Ethernet IP Router Example Design. It covers the general performance aspects of the protocols; cycle and instruction budgets; testing under different workloads; and performance measurements in both, simulation and hardware environments.

This document also attempts to analyze the amount of headroom available in this design for customers to add additional features by providing microengine and memory utilization metrics.

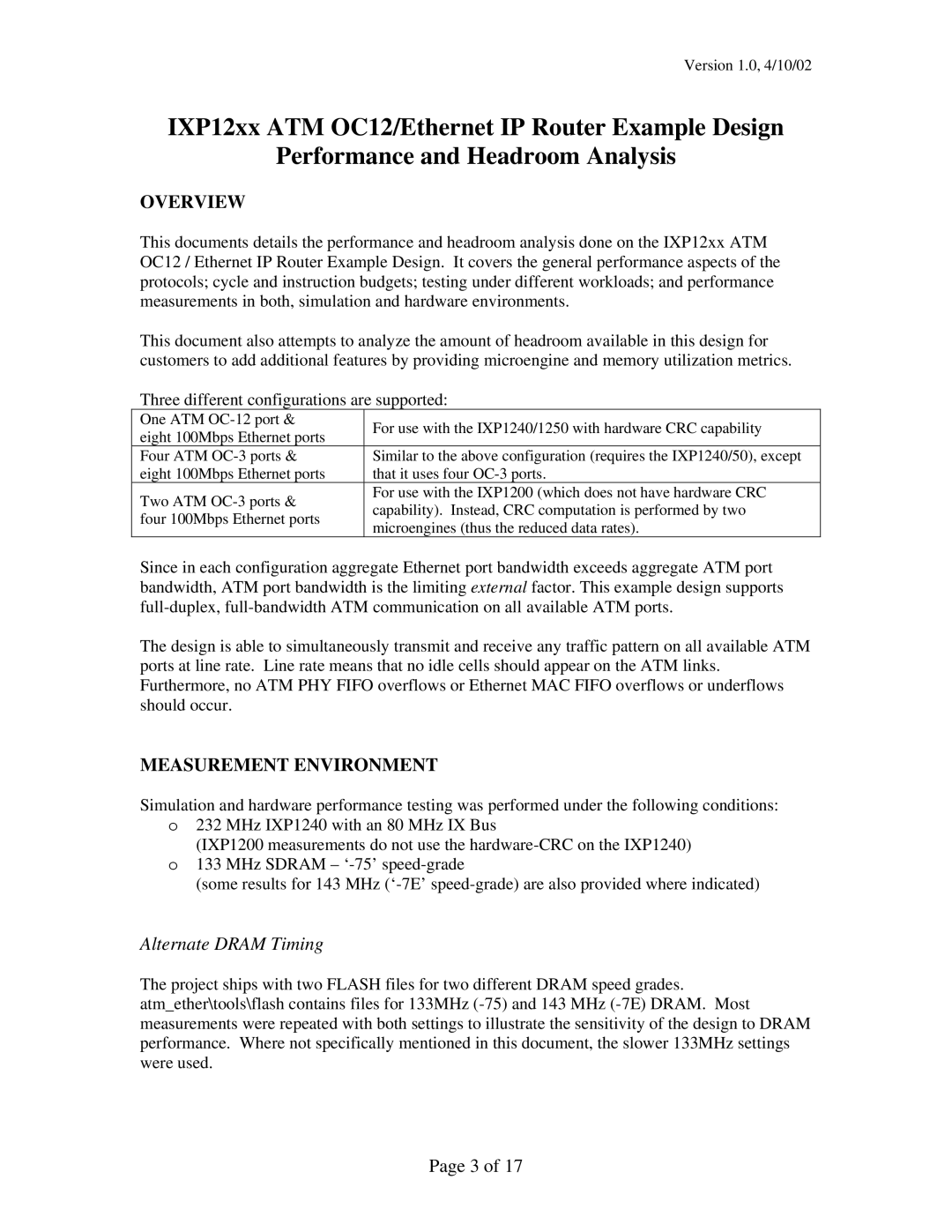

Three different configurations are supported:

One ATM | For use with the IXP1240/1250 with hardware CRC capability | |

eight 100Mbps Ethernet ports | ||

| ||

Four ATM | Similar to the above configuration (requires the IXP1240/50), except | |

eight 100Mbps Ethernet ports | that it uses four | |

Two ATM | For use with the IXP1200 (which does not have hardware CRC | |

capability). Instead, CRC computation is performed by two | ||

four 100Mbps Ethernet ports | ||

microengines (thus the reduced data rates). | ||

|

Since in each configuration aggregate Ethernet port bandwidth exceeds aggregate ATM port bandwidth, ATM port bandwidth is the limiting external factor. This example design supports

The design is able to simultaneously transmit and receive any traffic pattern on all available ATM ports at line rate. Line rate means that no idle cells should appear on the ATM links. Furthermore, no ATM PHY FIFO overflows or Ethernet MAC FIFO overflows or underflows should occur.

MEASUREMENT ENVIRONMENT

Simulation and hardware performance testing was performed under the following conditions:

o232 MHz IXP1240 with an 80 MHz IX Bus

(IXP1200 measurements do not use the

o133 MHz SDRAM –

(some results for 143 MHz

Alternate DRAM Timing

The project ships with two FLASH files for two different DRAM speed grades.

atm_ether\tools\flash contains files for 133MHz

Page 3 of 17