Version 1.0, 4/10/02

RESOURCE UTILIZATION AND HEADROOM ANALYSIS

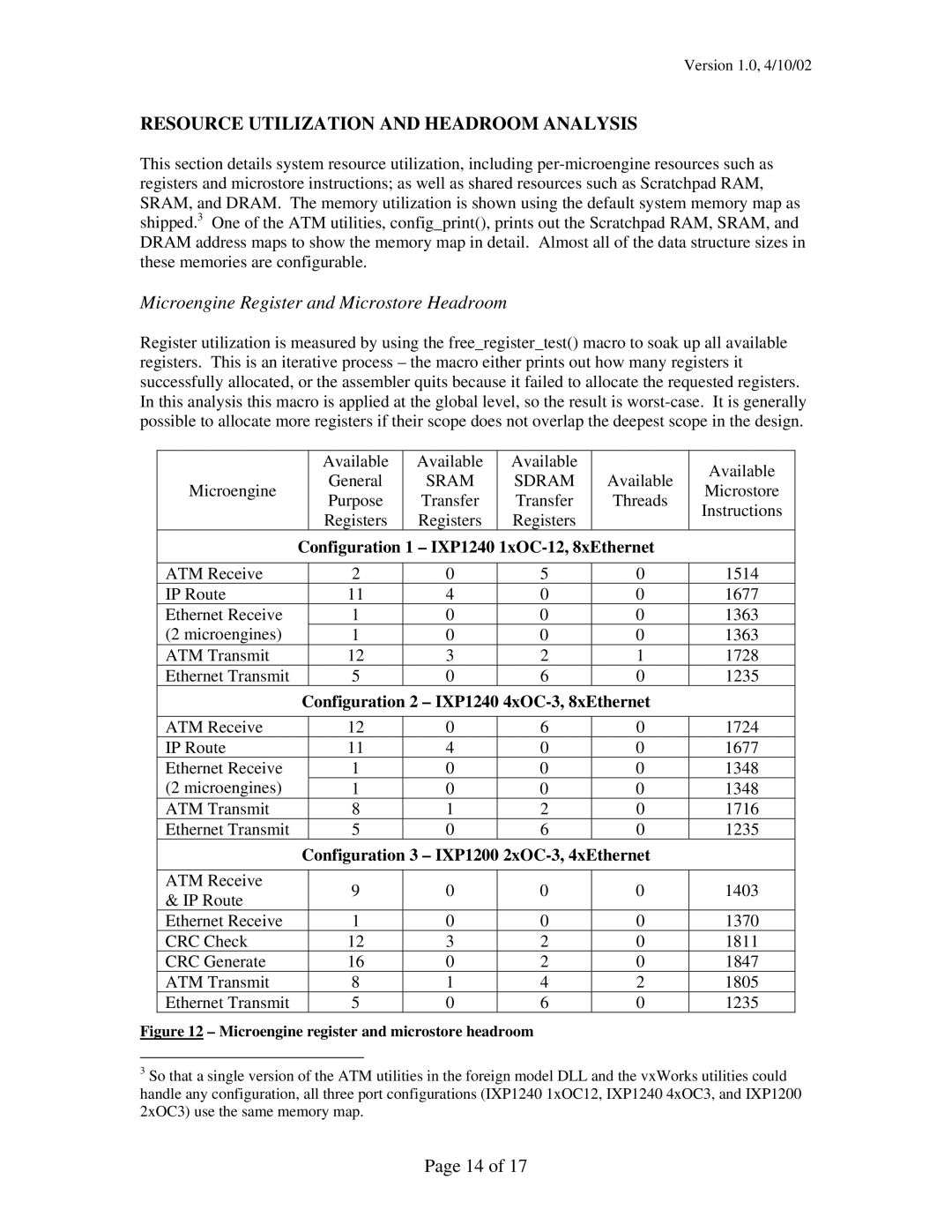

This section details system resource utilization, including

Microengine Register and Microstore Headroom

Register utilization is measured by using the free_register_test() macro to soak up all available registers. This is an iterative process – the macro either prints out how many registers it successfully allocated, or the assembler quits because it failed to allocate the requested registers. In this analysis this macro is applied at the global level, so the result is

|

| Available | Available | Available |

|

Microengine |

| General | SRAM | SDRAM | Available |

| Purpose | Transfer | Transfer | Threads | |

|

| ||||

|

| Registers | Registers | Registers |

|

| Configuration 1 – IXP1240 | ||||

|

|

|

|

| 0 |

ATM Receive |

| 2 | 0 | 5 | |

IP Route |

| 11 | 4 | 0 | 0 |

Ethernet Receive |

| 1 | 0 | 0 | 0 |

(2 microengines) |

| 1 | 0 | 0 | 0 |

ATM Transmit |

| 12 | 3 | 2 | 1 |

Ethernet Transmit |

| 5 | 0 | 6 | 0 |

| Configuration 2 – IXP1240 | ||||

|

|

|

| 0 | |

ATM Receive |

| 12 | 0 | 6 | |

IP Route |

| 11 | 4 | 0 | 0 |

Ethernet Receive |

| 1 | 0 | 0 | 0 |

(2 microengines) |

| 1 | 0 | 0 | 0 |

ATM Transmit |

| 8 | 1 | 2 | 0 |

Ethernet Transmit |

| 5 | 0 | 6 | 0 |

| Configuration 3 – IXP1200 | ||||

|

|

|

|

|

|

ATM Receive |

| 9 | 0 | 0 | 0 |

& IP Route |

| ||||

|

|

|

| 0 | |

Ethernet Receive |

| 1 | 0 | 0 | |

CRC Check |

| 12 | 3 | 2 | 0 |

CRC Generate |

| 16 | 0 | 2 | 0 |

ATM Transmit |

| 8 | 1 | 4 | 2 |

Ethernet Transmit |

| 5 | 0 | 6 | 0 |

Figure 12 – Microengine register and microstore headroom

Available

Microstore

Instructions

1514

1677

1363

1363

1728

1235

1724

1677

1348

1348

1716

1235

1403

1370

1811

1847

1805

1235

3So that a single version of the ATM utilities in the foreign model DLL and the vxWorks utilities could handle any configuration, all three port configurations (IXP1240 1xOC12, IXP1240 4xOC3, and IXP1200 2xOC3) use the same memory map.

Page 14 of 17