Preliminary Data Sheet, Rev. 5 |

| Instant USB |

September 1999 |

| 1284 Bridge |

|

|

|

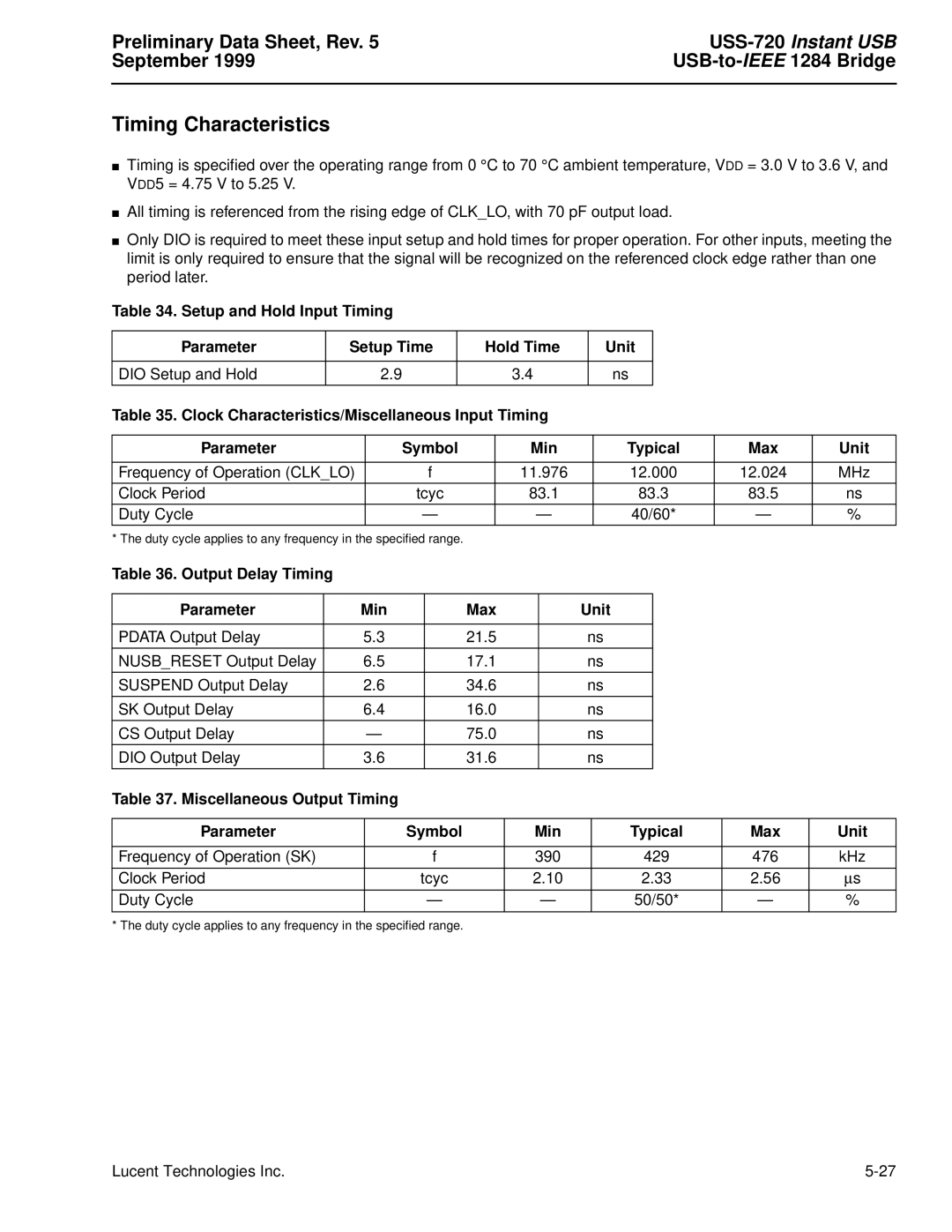

Timing Characteristics

■Timing is specified over the operating range from 0 °C to 70 °C ambient temperature, VDD = 3.0 V to 3.6 V, and VDD5 = 4.75 V to 5.25 V.

■All timing is referenced from the rising edge of CLK_LO, with 70 pF output load.

■Only DIO is required to meet these input setup and hold times for proper operation. For other inputs, meeting the limit is only required to ensure that the signal will be recognized on the referenced clock edge rather than one period later.

Table 34. Setup and Hold Input Timing |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

Parameter | Setup Time |

| Hold Time |

| Unit |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

DIO Setup and Hold | 2.9 |

|

| 3.4 |

| ns |

|

|

| ||

|

|

|

|

|

|

|

|

|

| ||

Table 35. Clock Characteristics/Miscellaneous Input Timing |

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| ||

Parameter |

|

| Symbol |

| Min |

| Typical | Max | Unit | ||

|

|

|

|

|

|

|

|

| |||

Frequency of Operation (CLK_LO) |

| f |

| 11.976 |

| 12.000 | 12.024 | MHz | |||

|

|

|

|

|

|

|

|

|

| ||

Clock Period |

|

| tcyc |

| 83.1 |

| 83.3 | 83.5 | ns | ||

|

|

|

|

|

|

|

|

|

| ||

Duty Cycle |

|

| — |

| — |

| 40/60* | — | % | ||

|

|

|

|

|

|

|

|

|

|

|

|

* The duty cycle applies to any frequency in the specified range.

Table 36. Output Delay Timing

Parameter | Min | Max | Unit |

|

|

|

|

PDATA Output Delay | 5.3 | 21.5 | ns |

|

|

|

|

NUSB_RESET Output Delay | 6.5 | 17.1 | ns |

|

|

|

|

SUSPEND Output Delay | 2.6 | 34.6 | ns |

SK Output Delay | 6.4 | 16.0 | ns |

|

|

|

|

CS Output Delay | — | 75.0 | ns |

|

|

|

|

DIO Output Delay | 3.6 | 31.6 | ns |

Table 37. Miscellaneous Output Timing

Parameter | Symbol | Min | Typical | Max | Unit |

|

|

|

|

|

|

Frequency of Operation (SK) | f | 390 | 429 | 476 | kHz |

|

|

|

|

|

|

Clock Period | tcyc | 2.10 | 2.33 | 2.56 | μs |

|

|

|

|

|

|

Duty Cycle | — | — | 50/50* | — | % |

|

|

|

|

|

|

* The duty cycle applies to any frequency in the specified range.

Lucent Technologies Inc. |