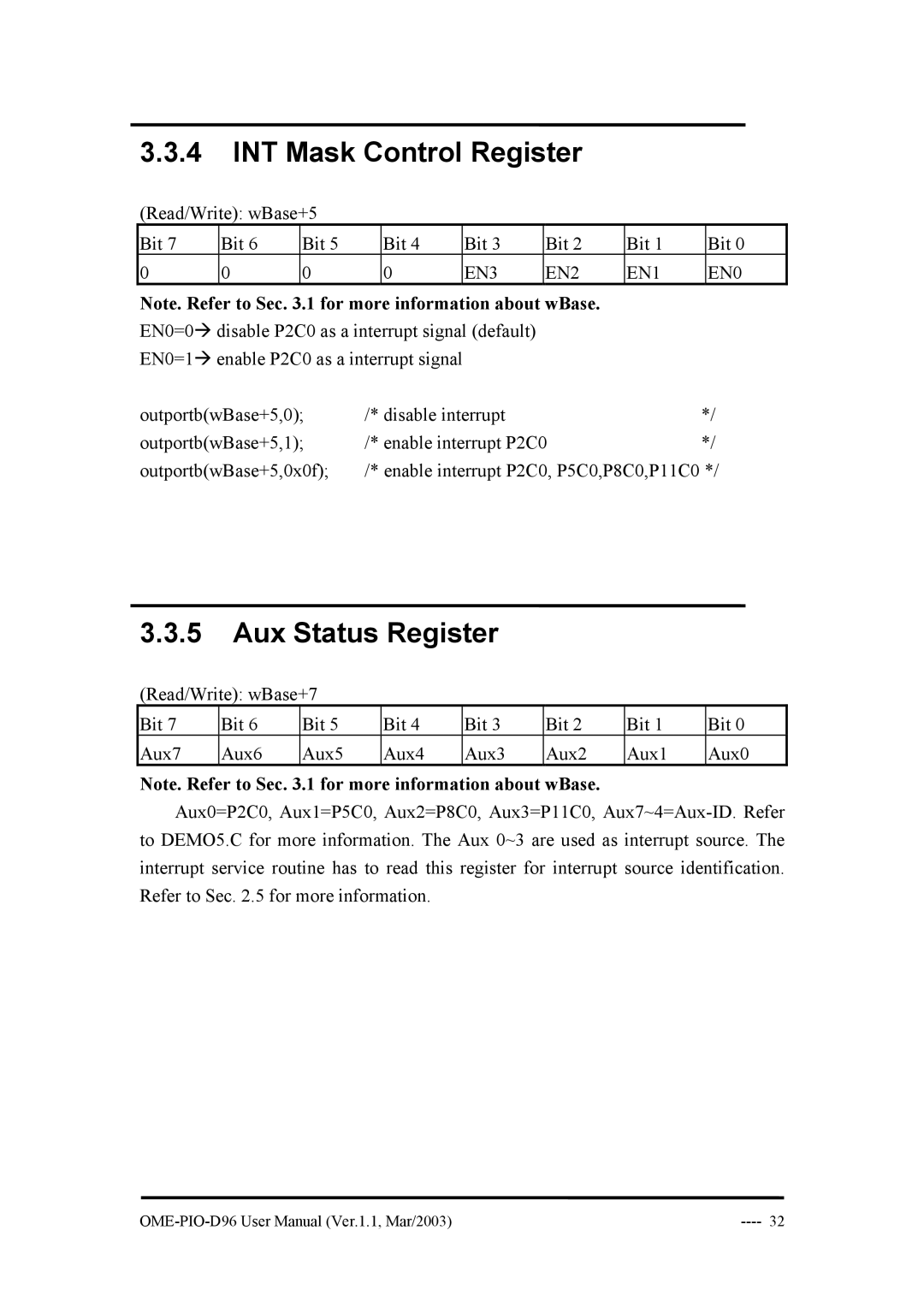

3.3.4INT Mask Control Register

(Read/Write): wBase+5

Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

0 | 0 | 0 | 0 | EN3 | EN2 | EN1 | EN0 |

Note. Refer to Sec. 3.1 for more information about wBase.

EN0=0Æ disable P2C0 as a interrupt signal (default)

EN0=1Æ enable P2C0 as a interrupt signal

outportb(wBase+5,0); | /* disable interrupt | */ |

outportb(wBase+5,1); | /* enable interrupt P2C0 | */ |

outportb(wBase+5,0x0f); | /* enable interrupt P2C0, P5C0,P8C0,P11C0 */ | |

3.3.5Aux Status Register

(Read/Write): wBase+7

Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

Aux7 | Aux6 | Aux5 | Aux4 | Aux3 | Aux2 | Aux1 | Aux0 |

Note. Refer to Sec. 3.1 for more information about wBase.

Aux0=P2C0, Aux1=P5C0, Aux2=P8C0, Aux3=P11C0,