SY-7IZB+

Edition March

SY-7IZB+

Version

7IZB+ Serial

Table of Contents

SY-7IZB+ Platform

SY-7IZB+ Motherboard Layout

Introduction

KEY Features

SY-7IZB+ Platform Features

JP9

These processors are not available yet for testing

Handling the Motherboard

Electrostatic Discharge Precautions

Preparations

Hardware Setup

Unpacking the Motherboard

CPU Installation

Installation Guide

CPU Fan Installation

Dimm

Sdram Memory Module Installation

Floppy Drive Installation

IDE Device Installation HDD, CD-ROM

Reset

Power LED & KeyLock

Front Panel Connections

Speaker

Acpi LED

ATX Power On/Off Switch

IDE LED

External Peripherals Connections

Serial Ports COM1/COM2

AT Keyboard

Parallel Port PRT1

Universal Serial Bus USB

PS/2 Mouse

Wake-On-LAN WOL

Other Connections

Infrared IR

Other Display Cards

CPU Cooling Fan

Cooling Fan Installation

Chassis Cooling Fan

AGP VGA Card

ATX Power Supply

PCI Audio Card

GND Ø Pay special care to the directionality

AT Power Supply

Setting

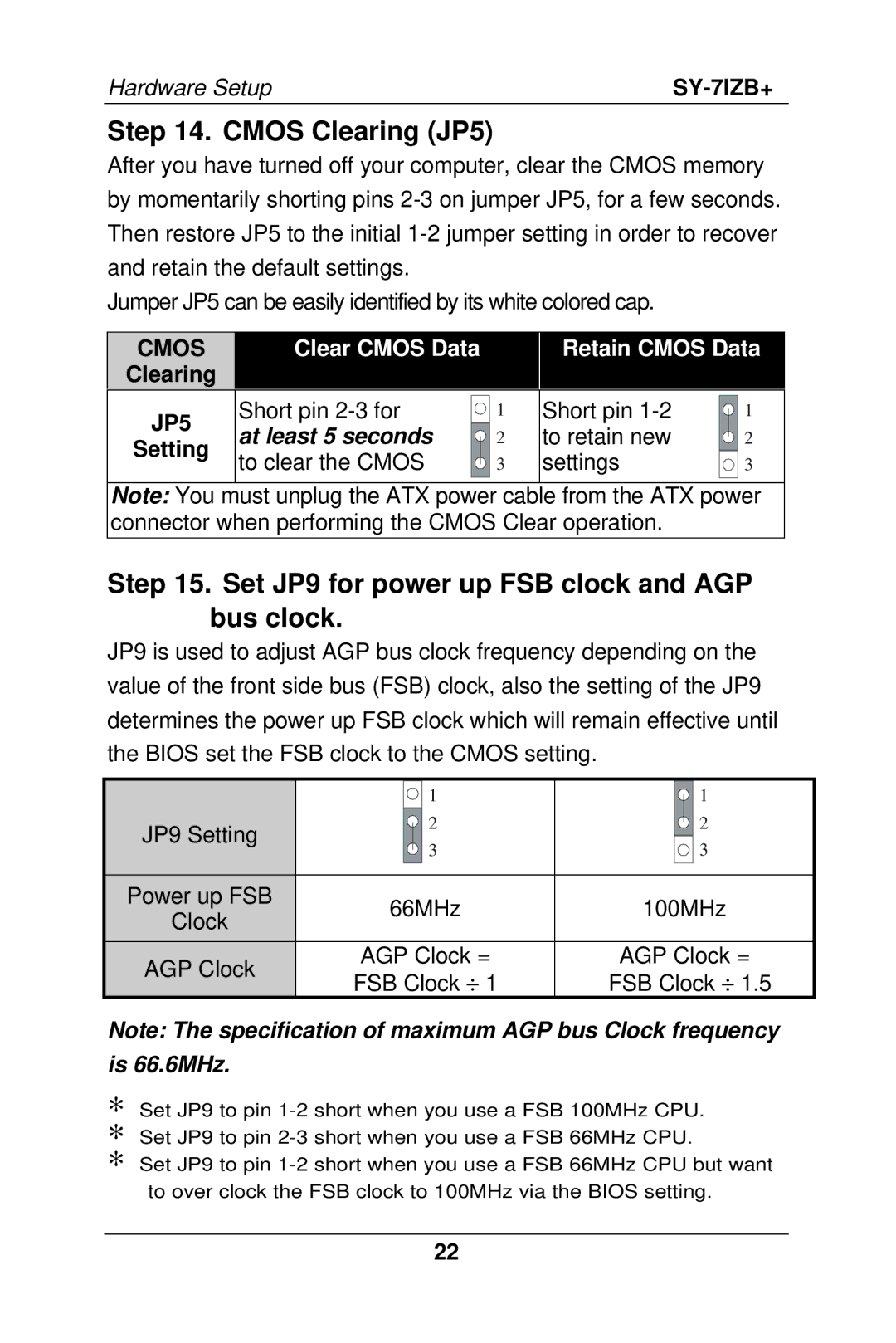

Set JP9 for power up FSB clock and AGP bus clock

Cmos Clearing JP5

JP5

Power On

Power-On by Keyboard Jumper JP10

Support Power

JP10 Setting

Select Load Setup Default

Quick Bios Setup

Select Soyo Combo Setup

Select Standard Cmos Setup

Power Off

Troubleshooting at First Start

Select Save & Exit Setup

Suspend Mode

Modifying selected items

Selecting items

Exit Without Saving

Save and Exit Setup

ROM PCI/ISA Bios Soyo Combo Setup Award SOFTWARE, INC

Soyo Combo Setup

CPU

Power on

Power-On by Ring/LAN Power-On by Alarm

Power Management PM Events Power button Setting Description

HotKey Soft-Off by

PWR-BTTN

Current

Current CPU Temperature

CPUFAN1

CPUFAN2 Speed Vcore, VTT, 3.3V, +12V, -5V, +5V, -12V,VBAT

Date & Time Display Setting Please Note

Standard Cmos Setup

Time

Primary Setting Description Secondary Master & Slave Type

Hard Disks Type & Mode

Floppy Drives Setting Description Drives a & B

Mode

Halt On

Video

ROM PCI/ISA Bios Bios Features Setup Award SOFTWARE, INC

Bios Features Setup

Boot Up NumLock Status

Cache Memory Options Setting Description CPU Internal Cache

External Cache

Typematic Settings Typematic Rate Setting Description

Security Option SettingDescription

Security Option

OS Select for DRAM64MB

When holding down a

Choose the rate at which Default

Typematic Delay

Choose how long after Default

Familiar with the Chipset

Chipset Features Setup

Features

Chipset Features Setup

Chipset Features

Chipset Features Setup

Passive Release Delayed Transaction AGP Aperture Size

Spread Spectrum Modulated

ROM PCI/ISA Bios Power Management Setup Award SOFTWARE, INC

Power Management Setup

PM Control by APM

Power Management Controls Setting Description Acpi function

Video Off Method

Video Off After Modem Use

Standby Mode

Doze Mode

Suspend Mode HDD Power

Down

Floppy Disk

IDE0, IDE1

Serial Port

Parallel Port

This option sets the Motherboards PCI Slots

PNP/PCI Configuration Setup

PNP/PCI

Assign IRQ For USB PnP OS Installed

PNP/PCI Configuration Setup

Slot 1/2/3/4 Use IRQ no Used MEM base addr

ROM PCI/ISA Bios Cmos Setup Utility Award SOFTWARE, INC

Load Setup Defaults

Integrated Peripherals

ROM PCI/ISA Bios Integrated Pweipherals Award SOFTWARD, INC

On-Chip PCI IDE Primary Secondary

IDE

RxD, TxD Active

Onboard Parallel Ports Setting Description

EPP Mode Select Pwron After PWR-Fail

ECP Mode use

DMA

Supervisor Password

SY-7IZB+

This diagram outlines the password selection procedure

User Password

IDE HDD Auto Detection

ROM PCI/ISA Bios Cmos Setup Utility Award SOFTWARE, INC

Insert the Soyo CD into the CD-ROM drive

Drivers Installation

Driver Installation Menu

Install Drivers and Utilities

Following drivers are available for Windows

Intel Southbridge Drivers

Short description of all available drivers follows

Soyo CD Xpress Utility

Enter the Soyo CD

Check the Latest Releases

Core voltage

Fan speed

Select which driver you want to install and click OK

![]() 1

1![]() 3

3