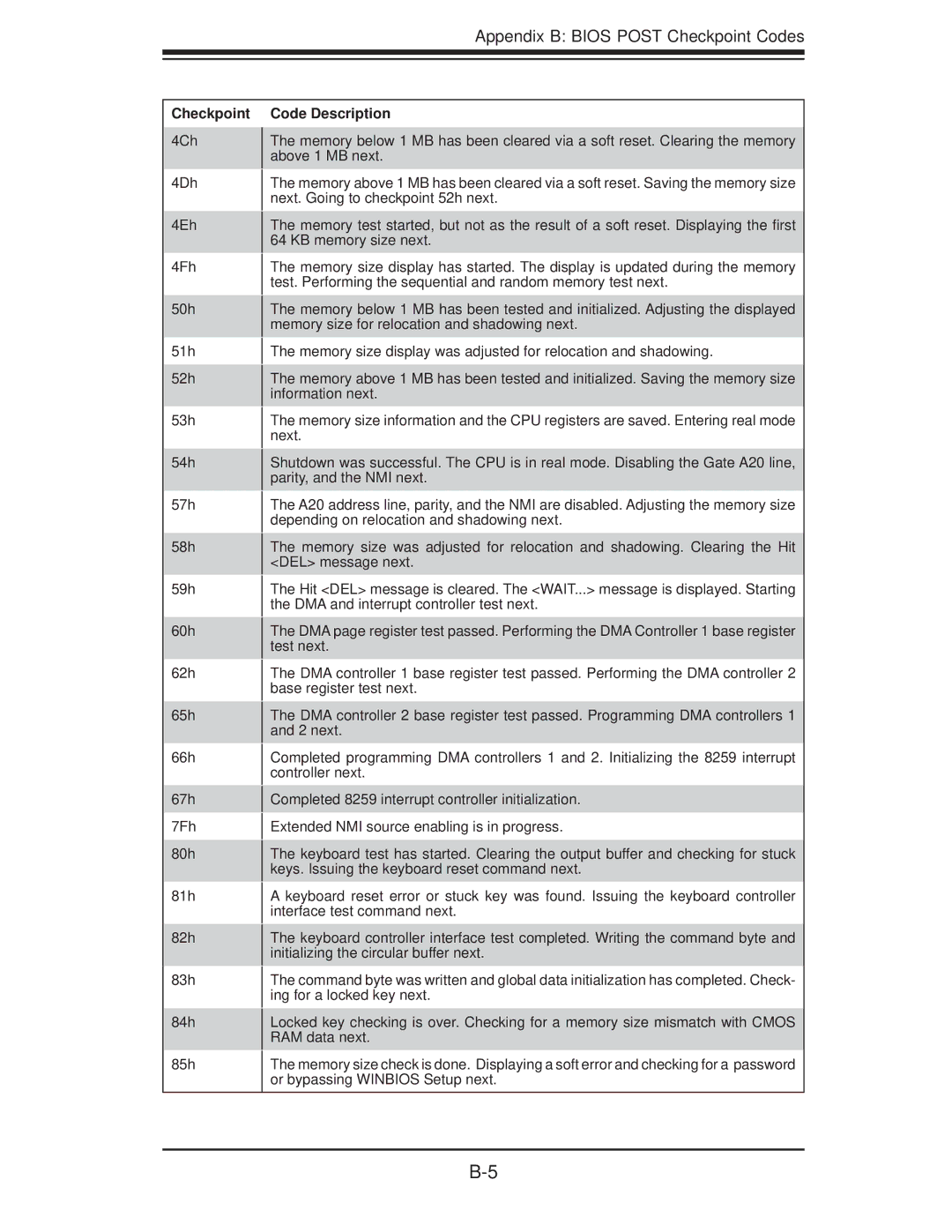

Appendix B: BIOS POST Checkpoint Codes

Checkpoint

4Ch

4Dh

4Eh

4Fh

50h

51h

52h

53h

54h

57h

58h

59h

60h

62h

65h

66h

67h

7Fh

80h

81h

82h

83h

84h

85h

Code Description

The memory below 1 MB has been cleared via a soft reset. Clearing the memory above 1 MB next.

The memory above 1 MB has been cleared via a soft reset. Saving the memory size next. Going to checkpoint 52h next.

The memory test started, but not as the result of a soft reset. Displaying the first 64 KB memory size next.

The memory size display has started. The display is updated during the memory test. Performing the sequential and random memory test next.

The memory below 1 MB has been tested and initialized. Adjusting the displayed memory size for relocation and shadowing next.

The memory size display was adjusted for relocation and shadowing.

The memory above 1 MB has been tested and initialized. Saving the memory size information next.

The memory size information and the CPU registers are saved. Entering real mode next.

Shutdown was successful. The CPU is in real mode. Disabling the Gate A20 line, parity, and the NMI next.

The A20 address line, parity, and the NMI are disabled. Adjusting the memory size depending on relocation and shadowing next.

The memory size was adjusted for relocation and shadowing. Clearing the Hit <DEL> message next.

The Hit <DEL> message is cleared. The <WAIT...> message is displayed. Starting the DMA and interrupt controller test next.

The DMA page register test passed. Performing the DMA Controller 1 base register test next.

The DMA controller 1 base register test passed. Performing the DMA controller 2 base register test next.

The DMA controller 2 base register test passed. Programming DMA controllers 1 and 2 next.

Completed programming DMA controllers 1 and 2. Initializing the 8259 interrupt controller next.

Completed 8259 interrupt controller initialization.

Extended NMI source enabling is in progress.

The keyboard test has started. Clearing the output buffer and checking for stuck keys. Issuing the keyboard reset command next.

A keyboard reset error or stuck key was found. Issuing the keyboard controller interface test command next.

The keyboard controller interface test completed. Writing the command byte and initializing the circular buffer next.

The command byte was written and global data initialization has completed. Check- ing for a locked key next.

Locked key checking is over. Checking for a memory size mismatch with CMOS RAM data next.

The memory size check is done. Displaying a soft error and checking for a password or bypassing WINBIOS Setup next.