32 | PCI Express® |

➔

PCI Express PHY

XIO1100

Get samples, datasheets, EVMs and app reports at: www.ti.com/sc/device/XIO1100

The XIO1100 is a PCI Express PHY, compliant with the PCI Express Base Specification Revision 1.1 that interfaces the PCI Express Media Access Layer (MAC) to a PCI Express serial link. It uses a modified version of the “PHY Interface for the PCI Express” (PIPE) interface also referred to as a

•The

•The

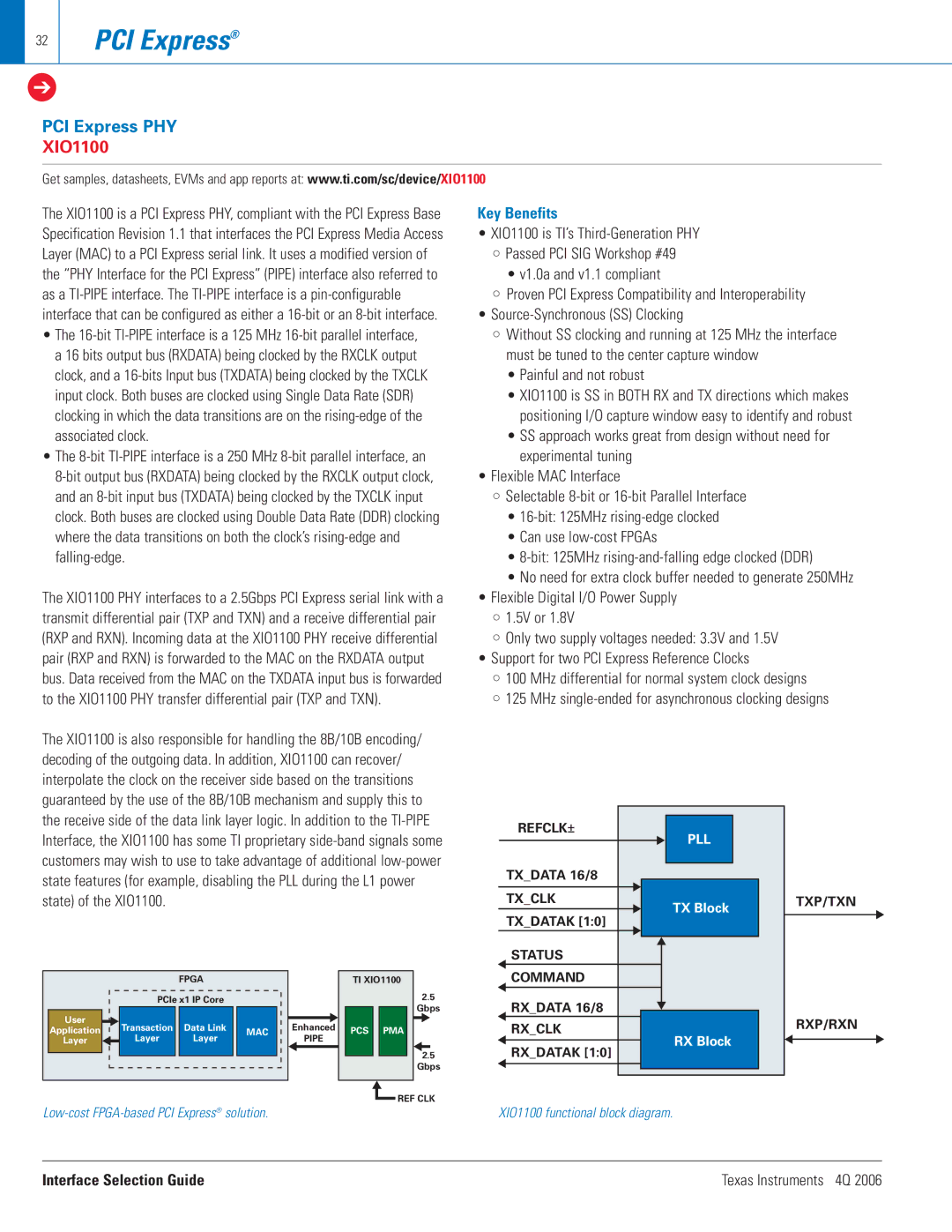

The XIO1100 PHY interfaces to a 2.5Gbps PCI Express serial link with a transmit differential pair (TXP and TXN) and a receive differential pair (RXP and RXN). Incoming data at the XIO1100 PHY receive differential pair (RXP and RXN) is forwarded to the MAC on the RXDATA output bus. Data received from the MAC on the TXDATA input bus is forwarded to the XIO1100 PHY transfer differential pair (TXP and TXN).

Key Benefits

•XIO1100 is TI’s

•Passed PCI SIG Workshop #49

•v1.0a and v1.1 compliant

•Proven PCI Express Compatibility and Interoperability

•

•Without SS clocking and running at 125 MHz the interface must be tuned to the center capture window

•Painful and not robust

•XIO1100 is SS in BOTH RX and TX directions which makes positioning I/O capture window easy to identify and robust

•SS approach works great from design without need for experimental tuning

•Flexible MAC Interface

•Selectable

•

•Can use

•

•No need for extra clock buffer needed to generate 250MHz

•Flexible Digital I/O Power Supply

•1.5V or 1.8V

•Only two supply voltages needed: 3.3V and 1.5V

•Support for two PCI Express Reference Clocks

•100 MHz differential for normal system clock designs

•125 MHz

The XIO1100 is also responsible for handling the 8B/10B encoding/ decoding of the outgoing data. In addition, XIO1100 can recover/ interpolate the clock on the receiver side based on the transitions guaranteed by the use of the 8B/10B mechanism and supply this to the receive side of the data link layer logic. In addition to the

REFCLK±

PLL

TX_DATA 16/8

TX_CLK

TX Block

TX_DATAK [1:0]

STATUS

TXP/TXN

|

|

|

| FPGA |

|

|

|

|

| PCIe x1 IP Core |

|

| |

|

|

|

|

|

|

|

| User |

| Transaction | Data Link |

|

|

| Application |

| MAC |

| ||

| Layer |

| Layer | Layer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Enhanced

PIPE

TI XIO1100

2.5

Gbps

PCS PMA

2.5

Gbps

![]() REF CLK

REF CLK

COMMAND

RX_DATA 16/8

RX_CLK

RX Block

RX_DATAK [1:0]

RXP/RXN

Interface Selection Guide | Texas Instruments 4Q 2006 |