PCI Express® | 31 |

|

|

|

|

x1 PCI Express® to 1394a OHCI Bridge XIO2200A

Get samples, datasheets, EVMs and app reports at:

www.ti.com/sc/device/XIO2200A

Key Features

•x1 PCI Express Primary Interface

•Supports two 1394a ports

•

•ExpressCard Reference Design supports two 1394a ports

•Internal dedicated PCI bus operates at

•Compact Footprint,

Key Benefits

•

•Advanced power management features

•

•Supports

•Compact footprint,

•EEPROM configuration allows a global unique ID for the 1394 fabric to load

Target Market

•ExpressCards

•PC Add-In Cards

•PC Motherboards

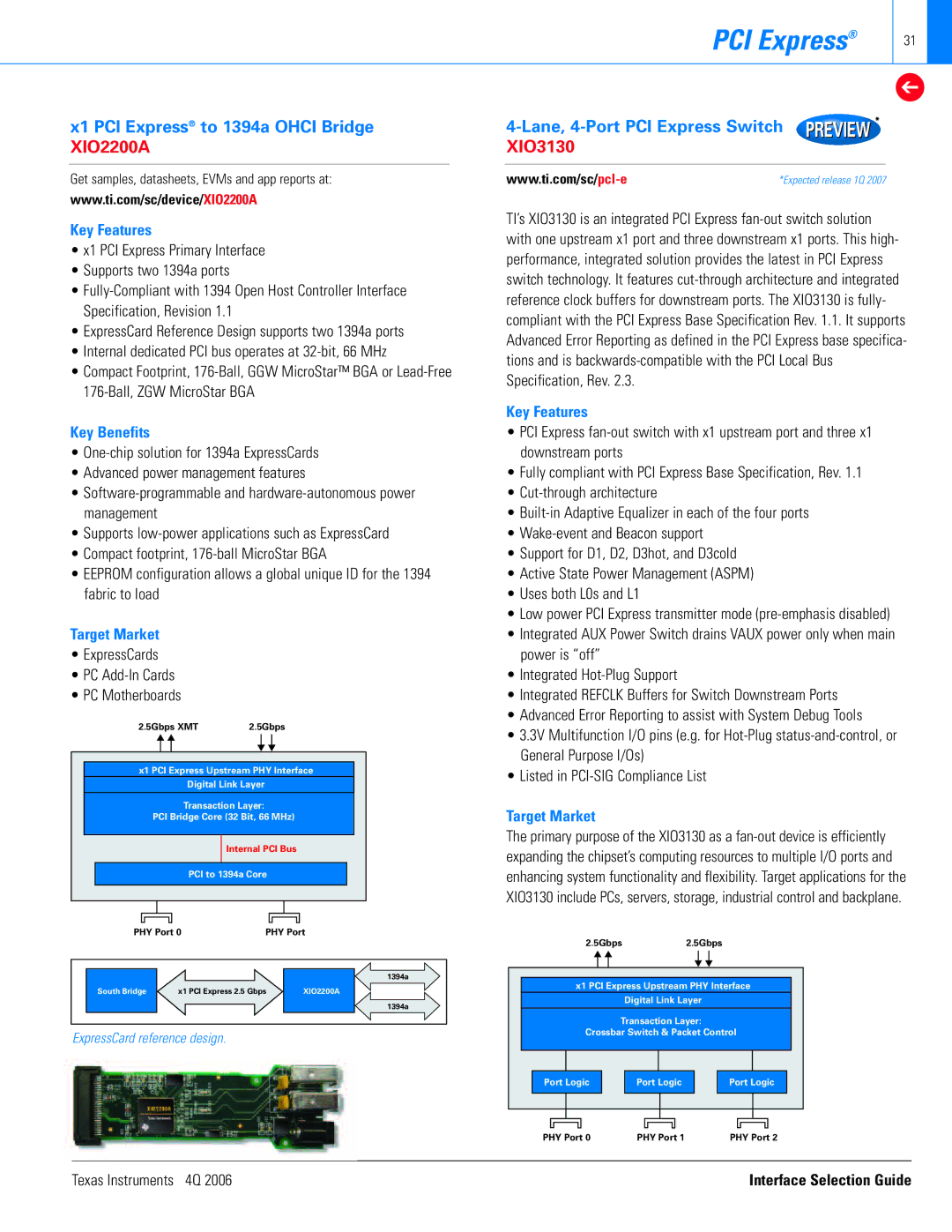

2.5Gbps XMT | 2.5Gbps |

x1 PCI Express Upstream PHY Interface

Digital Link Layer

Transaction Layer:

PCI Bridge Core (32 Bit, 66 MHz)

Internal PCI Bus

PCI to 1394a Core

PHY Port 0 | PHY Port |

|

|

| 1394a |

outhS Bridge | x1 PCI Express 2.5 Gbps | XI0 | O22 0A |

|

|

| 1394a |

ExpressCard reference design.

➔

XIO3130

*Expected release 1Q 2007 |

TI’s XIO3130 is an integrated PCI Express

Key Features

•PCI Express

•Fully compliant with PCI Express Base Specification, Rev. 1.1

•

•

•

•Support for D1, D2, D3hot, and D3cold

•Active State Power Management (ASPM)

•Uses both L0s and L1

•Low power PCI Express transmitter mode

•Integrated AUX Power Switch drains VAUX power only when main power is “off”

•Integrated

•Integrated REFCLK Buffers for Switch Downstream Ports

•Advanced Error Reporting to assist with System Debug Tools

•3.3V Multifunction I/O pins (e.g. for

•Listed in

Target Market

The primary purpose of the XIO3130 as a

2.5Gbps2.5Gbps

x1 PCI Express Upstream PHY Interface

Digital Link Layer

Transaction Layer:

Crossbar Switch & Packet Control

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Port Logic |

| Port Logic |

| Port Logic |

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PHY Port 0 |

| PHY Port 1 |

| PHY Port 2 | |||||||||||

Texas Instruments 4Q 2006 | Interface Selection Guide |