Design Considerations

Primary

GTLP (Gunning Transceiver Logic Plus) | 39 |

|

|

| ➔ |

Speed — The speed of the GTLP family in parallel backplanes is 4x that of traditional logic. Optimized output

Voltage Range — The GTLP family operates at 3.3 V and with

Drive — The GTLP family provides

Signal

True Live Insertion — GTLP backplane drivers allow for Level 3 isolation and true live- insertion capability. Level 1 isolation, partial

down the host system and without suspending signaling. Level 3 isolation, live insertion: for live insertion both IOFF and PU3S circuitry are needed and the board I/Os must be precharged to

Secondary

Compatibility — GTLP provides an easy migration path from traditional backplane logic like ABT, FCT, LVT, ALVT, LVC and FB+.

Portfolio — TI offers the broadest GTLP portfolio in the industry, with both

Packaging — TI offers GTLP in a

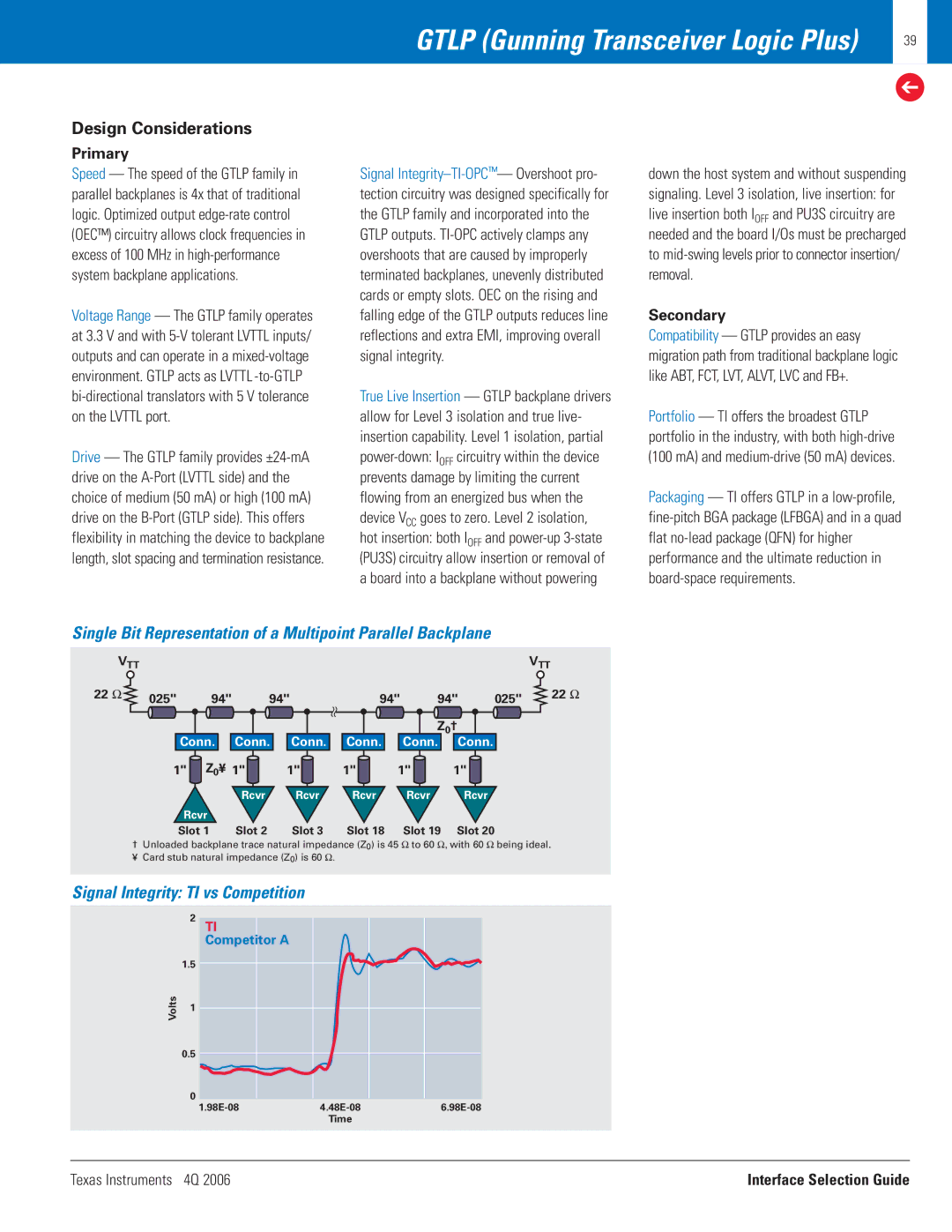

Single Bit Representation of a Multipoint Parallel Backplane

VTT |

|

|

|

|

|

|

| VTT |

22 Ω | 0.25" | 94". | 94". | 94". | 94". | 025". | 22 Ω | |

|

| |||||||

|

|

|

|

|

| Z0† |

|

|

| Conn. Conn. Conn. Conn. Conn. Conn. |

|

| |||||

| 1" Z0¥ 1" | 1" | 1" | 1" | 1" |

|

| |

|

| Rcvr | Rcvr | Rcvr | Rcvr | Rcvr |

|

|

| Rcvr |

|

|

|

|

|

|

|

| Slot 1 | Slot 2 | Slot 3 | Slot 18 | Slot 19 Slot 20 |

|

| |

†Unloaded backplane trace natural impedance (Z0) is 45 Ω to 60 Ω, with 60 Ω being ideal. ¥ Card stub natural impedance (Z0) is 60 Ω.

Signal Integrity: TI vs Competition

Volts

2

TI

Competitor A

1.5

1

0.5

0

| Time |

|

Texas Instruments 4Q 2006 | Interface Selection Guide |