30 | PCI Express® |

➔

PCI Express® Bridge Chip

XIO2000A

Get samples, datasheets, EVMs and app reports at: www.ti.com/sc/device/XIO2000A

TI’s PCI Express bridge chip, the XIO2000A, is an industry first. It is designed for seamless migration from the legacy PCI to the PCI Express interface. It bridges an x1 PCI Express bus to a

2.3interface. The chip’s design enables PC and I/O

Key Features

•Compliant with PCI Express to

•Compliant with PCI Express Base Specification 1.0a

•Compliant with PCI Local Bus Specification rev 2.3

•Utilizes 100 MHz differential PCI Express Common Reference Clock or 125 MHz

•Full PCI Local Bus 66

•Wake/Beacon Event Support

•Robust Architecture to Minimize Latency

Key Benefits

• |

• Improves jitter tolerance thereby |

reliably increasing PCB trace, or cable |

length, supported by the XIO2000 |

• Seven buffered PCI clock outputs |

(33 MHz or 66 MHz) |

• Reduces external components, costs |

and premium board space |

• |

|

• Customizes to meet the needs of high- |

performance or |

• Proven compatibility with various PCI |

Express chipsets and PCI |

• Rigorous field testing with major root |

| PCI Express | PCI Express | |

| Transmitter |

| Receiver |

Power |

|

| GPIO |

Mgmt |

|

| |

|

|

| |

Clock | Configuration and | Serial | |

Generator |

| Memory Register | EEPROM |

Reset |

|

| Serial IRQ |

Controller |

|

| |

|

|

| |

|

| PCI Bus Interface |

|

complex device and numerous PCI |

• Compact footprint |

• Allows placement in ExpressCard and |

• Advanced power management |

features |

• Software programmable and hardware |

autonomous power management |

features for |

such as ExpressCard |

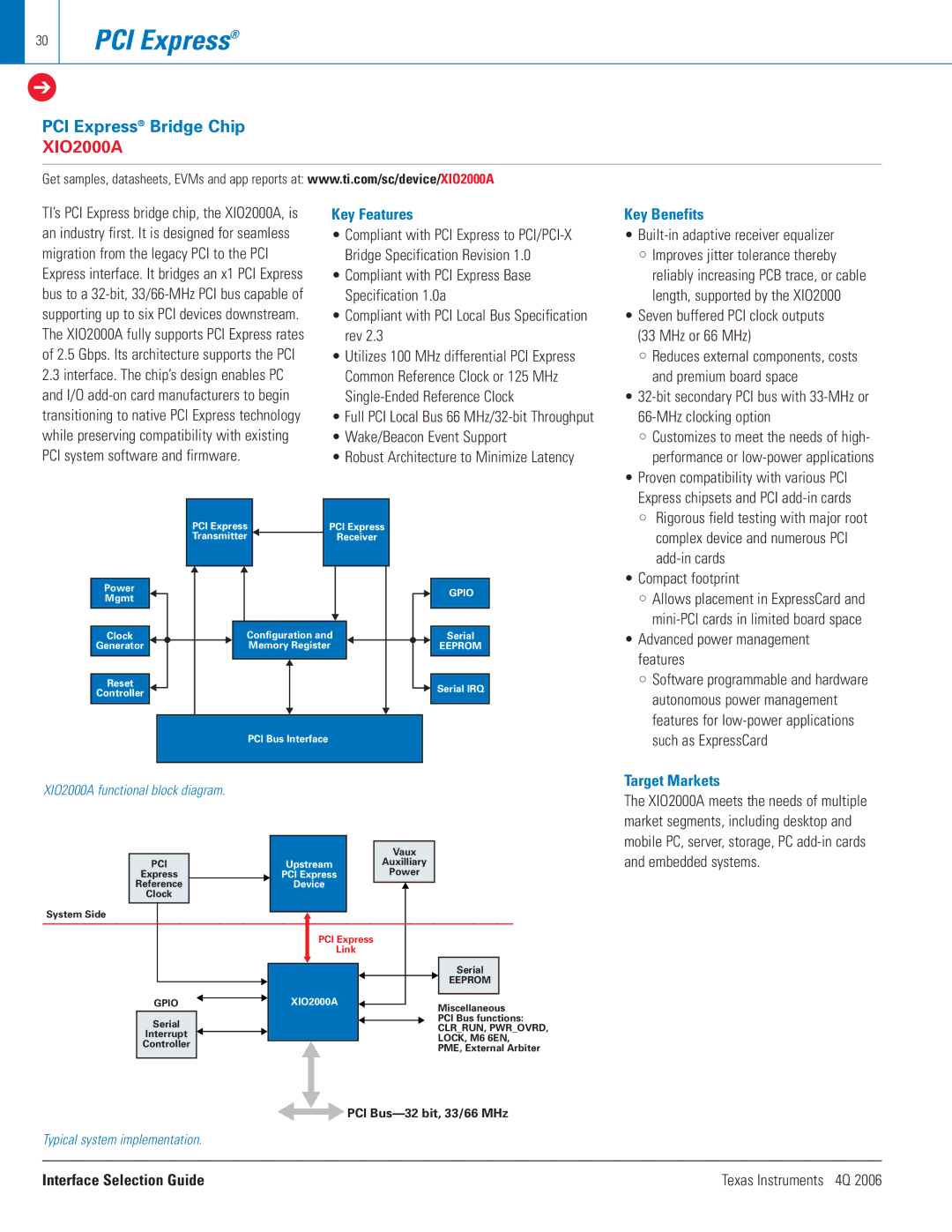

XIO2000A functional block diagram.

|

| Vaux |

PCI | Upstream | Auxilliary |

Express | PCI Express | Power |

Reference | Device |

|

Clock |

|

|

System Side |

|

|

| PCI Express |

|

| Link |

|

|

| Serial |

|

| EEPROM |

GPIO | XIO2000A | Miscellaneous |

|

| |

Serial |

| PCI Bus functions: |

| CLR_RUN, PWR_OVRD, | |

Interrupt |

| |

| LOCK, M6 6EN, | |

Controller |

| |

| PME, External Arbiter | |

|

|

Target Markets

The XIO2000A meets the needs of multiple market segments, including desktop and mobile PC, server, storage, PC

PCI

Typical system implementation.

Interface Selection Guide | Texas Instruments 4Q 2006 |