UARTs (Universal Asynchronous Receiver/Transmitters) | 17 |

|

➔

UART Selection Guide

|

|

| Voltage | Characterized |

|

|

Device | Channel(s) | FIFOs | (V) | Temp. (°C) | Package(s) | Description |

Universal Asynchronous Receiver/Transmitters (UARTs)

Price*

TL16C2550 | 2 | 1.8/2.5/3.3/5 | 32 QFN, 44 PLCC, | Dual UART with Programmable | 2.80 | ||

|

|

|

|

| 48 TQFP |

|

|

TL16C2552 | 2 | 1.8/2.5/3.3/5 | 32 QFN, 44 PLCC | Dual UART with Programmable | 3.00 | ||

TL16C2752 | 2 | 1.8/2.5/3.3/5 | — | 44 PLCC | Dual UART with Customizable Trigger Levels | Call | |

TL16C450 | 1 | None | 5 | 0 to 70 | 40 DIP, 44 PLCC | Single UART | 1.50 |

TL16C451 | 1 | None | 5 | 0 to 70 | 68 PLCC | Single UART with Parallel Port | 2.50 |

TL16C452 | 2 | None | 5 | 0 to 70 | 68 PLCC | Dual UART with Parallel Port | 2.55 |

TL16C550C | 1 | 3.3/5 | 40 DIP, 44 PLCC, | Single UART with Hardware Autoflow Control | 1.75 | ||

|

|

|

|

| 48 LQFP, 48 TQFP |

|

|

TL16C550D | 1 | 2.5/3.3/5 | 32 QFN | Single UART with Hardware Autoflow Control | 1.75 | ||

|

|

|

|

| 48 LQFP, 48 TQFP |

|

|

TL16C552A | 2 | 5 | 68 PLCC, 80 TQFP | Dual UART with Parallel Port | 3.85 | ||

TL16C554A | 4 | 5 | 68 PLCC, 80 LQFP | Quad UART with Hardware Autoflow Control | 6.00 | ||

TL16C750 | 1 | 5 | 44 PLCC, 64 LQFP | Single UART with Hardware Autoflow Control, | 3.70 | ||

TL16C752B | 2 | 3.3 | 48 LQFP, 48 TQFP | Dual UART with Hardware Autoflow Control, | 3.10 | ||

TL16C754B | 4 | 3.3/5 | 68 PLCC, 80 LQFP | Dual UART with Hardware Autoflow Control, | 8.35 | ||

TL16PC564B/BLV | 1 | 3.3/5 | 0 to 70 | 100 BGA, 100 LQFP | Single UART with PCMCIA Interface | 5.90/6.10 | |

TL16PIR552 | 2 | 5 | 0 to 70 | 80 QFP | Dual UART with Selectable IR & 1284 Modes | 6.10 |

*Suggested resale price in U.S. dollars in quantities of 1,000.

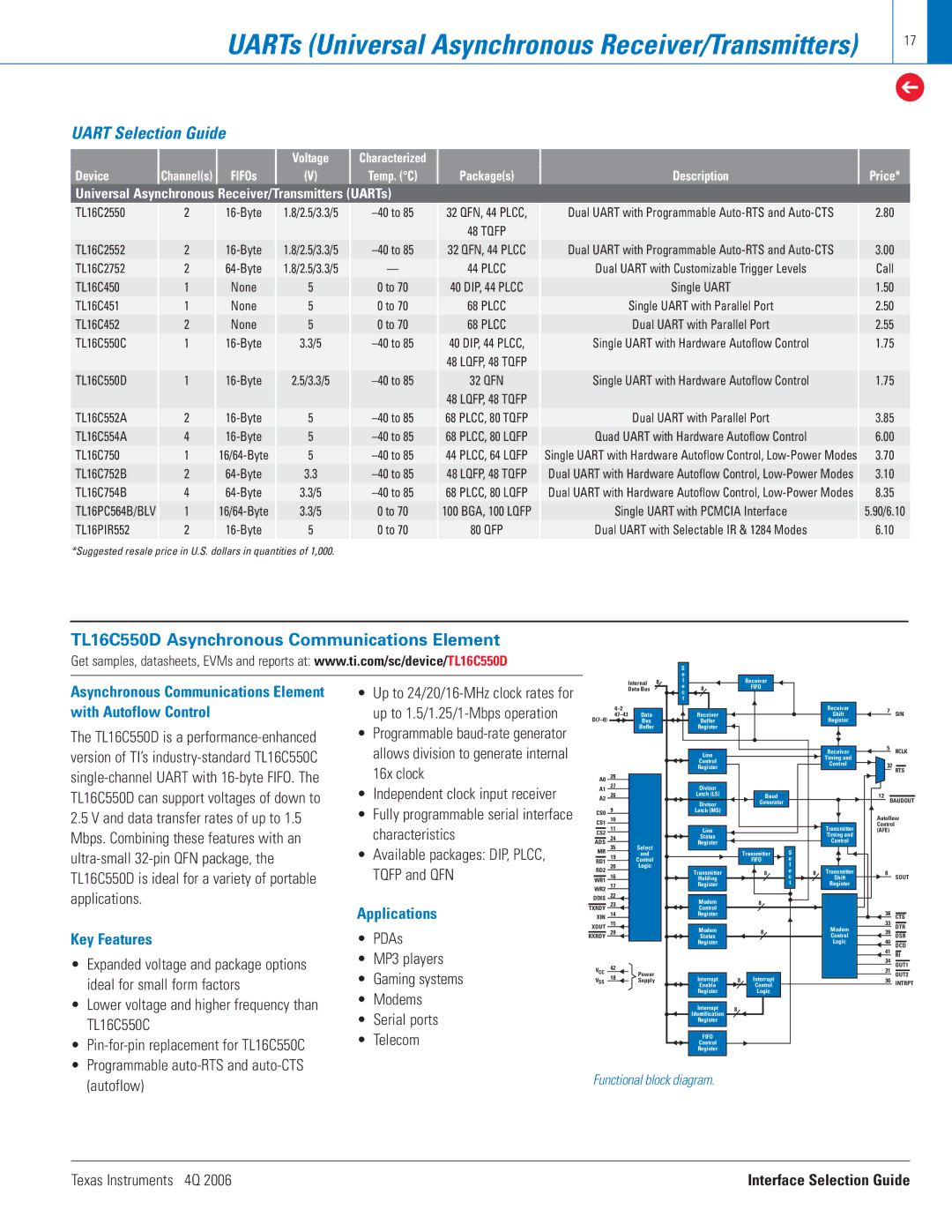

TL16C550D Asynchronous Communications Element

Get samples, datasheets, EVMs and reports at: www.ti.com/sc/device/TL16C550D

Asynchronous Communications Element with Autoflow Control

The TL16C550D is a

2.5V and data transfer rates of up to 1.5 Mbps. Combining these features with an

Key Features

•Expanded voltage and package options ideal for small form factors

•Lower voltage and higher frequency than TL16C550C

•

•Programmable

•Up to

•Programmable

•Independent clock input receiver

•Fully programmable serial interface characteristics

•Available packages: DIP, PLCC, TQFP and QFN

Applications

•PDAs

•MP3 players

•Gaming systems

•Modems

•Serial ports

•Telecom

|

|

|

| S |

|

|

|

|

|

|

|

|

|

|

|

| e |

|

|

|

|

|

|

|

|

|

| Internal | 8 | l |

|

| Receiver |

|

|

|

|

|

|

| Data Bus |

| e | 8 |

| FIFO |

|

|

|

|

|

|

|

| c |

|

|

|

|

|

|

| ||

|

|

|

| t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Receiver | 7 | SIN | |

Data |

|

| Receiver |

|

|

|

| Shift | ||||

| Bus |

|

| Buffer |

|

|

|

| Register |

|

| |

|

| Buffer |

|

| Register |

|

|

|

|

|

|

|

|

|

|

|

| Line |

|

|

|

| Receiver | 5 | RCLK |

|

|

|

|

|

|

|

|

| Timing and |

|

| |

|

|

|

|

| Control |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| Control | 32 |

| |

|

|

|

|

| Register |

|

|

|

| RTS | ||

|

|

|

|

|

|

|

|

|

| |||

| 28 |

|

|

|

|

|

|

|

|

|

| |

A0 |

|

|

|

|

|

|

|

|

|

|

| |

A1 | 27 |

|

|

| Divisor |

|

|

|

|

|

|

|

A2 | 26 |

|

|

| Latch (LS) |

| Baud |

|

|

| 12 |

|

|

|

|

|

| Divisor |

| Generator |

|

|

| BAUDOUT | |

CS0 | 9 |

|

|

| Latch (MS) |

|

|

|

|

| Autoflow | |

CS1 | 10 |

|

|

|

|

|

|

|

|

| ||

11 |

|

|

|

|

|

|

|

| Transmitter | Control |

| |

CS2 |

|

|

| Line |

|

|

|

| (AFE) |

| ||

24 |

|

|

| Status |

|

|

|

| Timing and |

|

| |

ADS | Select |

|

| Register |

|

|

|

| Control |

|

| |

MR | 35 |

|

|

|

|

| S |

|

|

|

| |

19 | and |

|

|

|

| Transmitter |

|

|

|

| ||

RD1 | Control |

|

|

|

| FIFO | e |

|

|

|

| |

20 | Logic |

|

|

|

|

| l |

|

|

|

| |

RD2 |

|

|

|

|

|

|

|

|

| |||

|

| Transmitter |

| 8 | e | 8 | Transmitter | 8 |

| |||

WR1 | 16 |

|

|

| Holding |

|

| c |

| Shift |

| SOUT |

17 |

|

|

| Register |

|

| t |

| Register |

|

| |

WR2 |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |||

DDIS | 22 |

|

|

| Modem |

| 8 |

|

|

|

|

|

| 23 |

|

|

|

|

|

|

|

|

| ||

TXRDY |

|

|

| Control |

|

|

|

| 38 |

| ||

XIN | 14 |

|

|

| Register |

|

|

|

|

| CTS | |

XOUT | 15 |

|

|

| Modem |

| 8 |

|

| Modem | 33 | DTR |

| 29 |

|

|

|

|

|

| 39 |

| |||

RXRDY |

|

|

| Status |

|

|

| Control | DSR | |||

|

|

|

|

| Register |

|

|

|

| Logic | 40 | DCD |

|

|

|

|

|

|

|

|

|

|

| 41 | RI |

VCC | 42 |

|

|

|

|

|

|

|

|

| 34 | OUT1 |

Power |

|

|

|

|

|

|

|

| 31 | OUT2 | ||

18 |

|

| Interrupt | 8 | Interrupt |

|

|

| ||||

VSS | Supply |

|

|

|

|

| 30 | INTRPT | ||||

|

|

| Enable | Control |

|

|

| |||||

|

|

|

|

| Register |

| Logic |

|

|

|

|

|

|

|

|

|

| Interrupt | 8 |

|

|

|

|

|

|

|

|

|

|

| Identification |

|

|

|

|

|

|

|

|

|

|

|

| Register |

|

|

|

|

|

|

|

|

|

|

|

| FIFO |

|

|

|

|

|

|

|

|

|

|

|

| Control |

|

|

|

|

|

|

|

|

|

|

|

| Register |

|

|

|

|

|

|

|

Functional block diagram.

Texas Instruments 4Q 2006 | Interface Selection Guide |