TAS5010−5112F2EVM Features

1.1TAS5010−5112F2EVM Features

-PurePath Digital™ reference design (double-sided plated-through PCB layout)

-S/PDIF receiver with coaxial and optical input (sampling rate = 32 kHz – 192 kHz)

-I2S audio interface (sampling rate: 32 kHz – 96 kHz)

-On-board volume control

-Auto-mute function

-Self-contained short circuit and temperature protection system

-Digital audio processor (DAP), which include 24-bit volume control, digital gain, bass and treble control, parametric equalization, dedicated speaker equalization, loudness control, and adjustable dynamic range compression/expansion.

-DAP control through PC software (DCT software from Texas Instruments)

-Default DAP settings is downloaded to an EEPROM with the DCT software

-Analog line input (use internal analog-to-digital converter in DAP)

-Analog line output (use internal digital-to-analog converter in DAP)

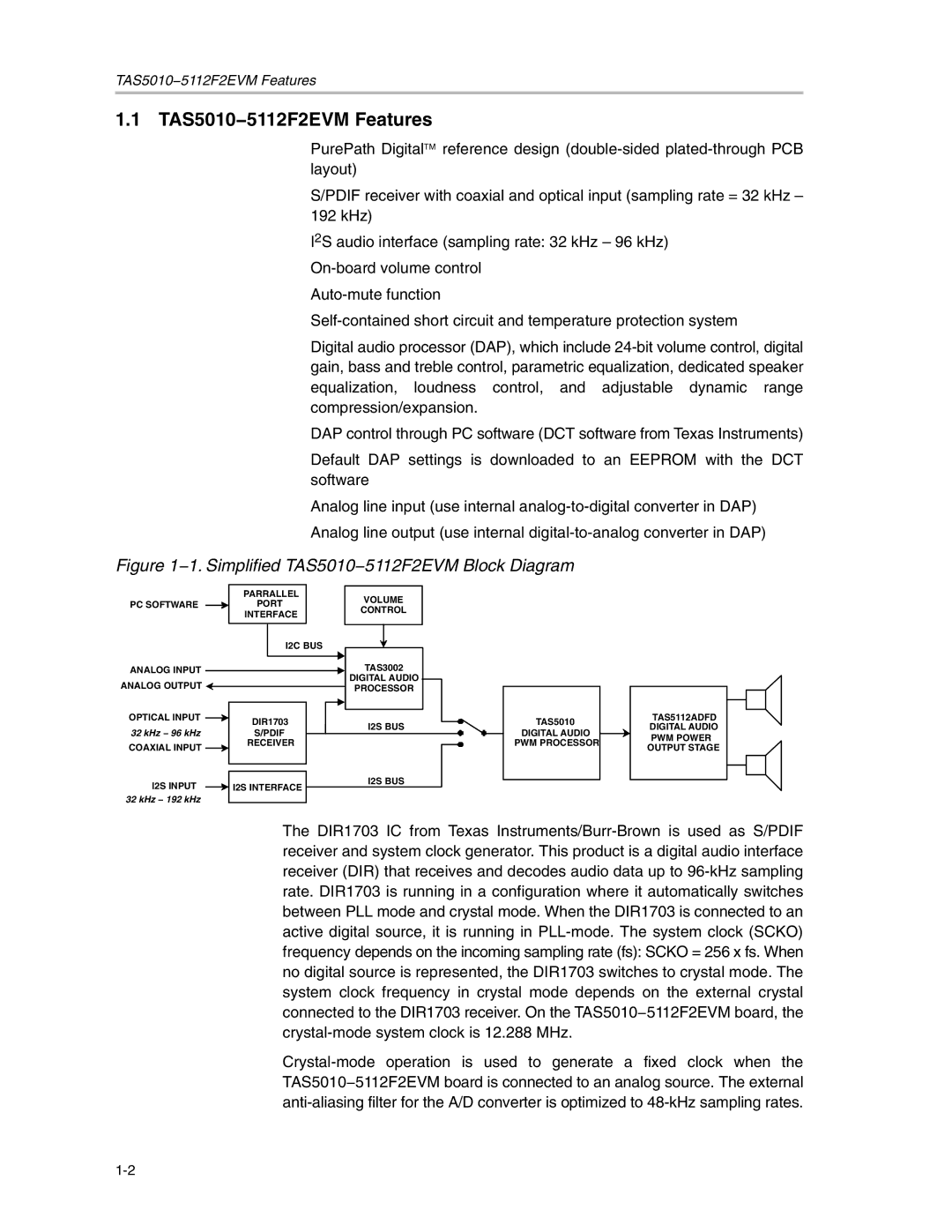

Figure 1−1. Simplified TAS5010−5112F2EVM Block Diagram

| | PARRALLEL | VOLUME |

| PC SOFTWARE | PORT |

| CONTROL |

| | INTERFACE |

| | |

| | I2C BUS | |

| ANALOG INPUT | | TAS3002 |

| ANALOG OUTPUT | | DIGITAL AUDIO |

| | PROCESSOR |

| OPTICAL INPUT | DIR1703 | I2S BUS |

| |

| 32 kHz − 96 kHz | S/PDIF |

| |

| COAXIAL INPUT | RECEIVER | |

| | |

| I2S INPUT | I2S INTERFACE | I2S BUS |

| |

| 32 kHz − 192 kHz | | |

TAS5010

DIGITAL AUDIO

PWM PROCESSOR

TAS5112ADFD

DIGITAL AUDIO PWM POWER OUTPUT STAGE

The DIR1703 IC from Texas Instruments/Burr-Brown is used as S/PDIF receiver and system clock generator. This product is a digital audio interface receiver (DIR) that receives and decodes audio data up to 96-kHz sampling rate. DIR1703 is running in a configuration where it automatically switches between PLL mode and crystal mode. When the DIR1703 is connected to an active digital source, it is running in PLL-mode. The system clock (SCKO) frequency depends on the incoming sampling rate (fs): SCKO = 256 x fs. When no digital source is represented, the DIR1703 switches to crystal mode. The system clock frequency in crystal mode depends on the external crystal connected to the DIR1703 receiver. On the TAS5010−5112F2EVM board, the crystal-mode system clock is 12.288 MHz.

Crystal-mode operation is used to generate a fixed clock when the TAS5010−5112F2EVM board is connected to an analog source. The external anti-aliasing filter for the A/D converter is optimized to 48-kHz sampling rates.