Digital I/O

3.5 Digital I/O

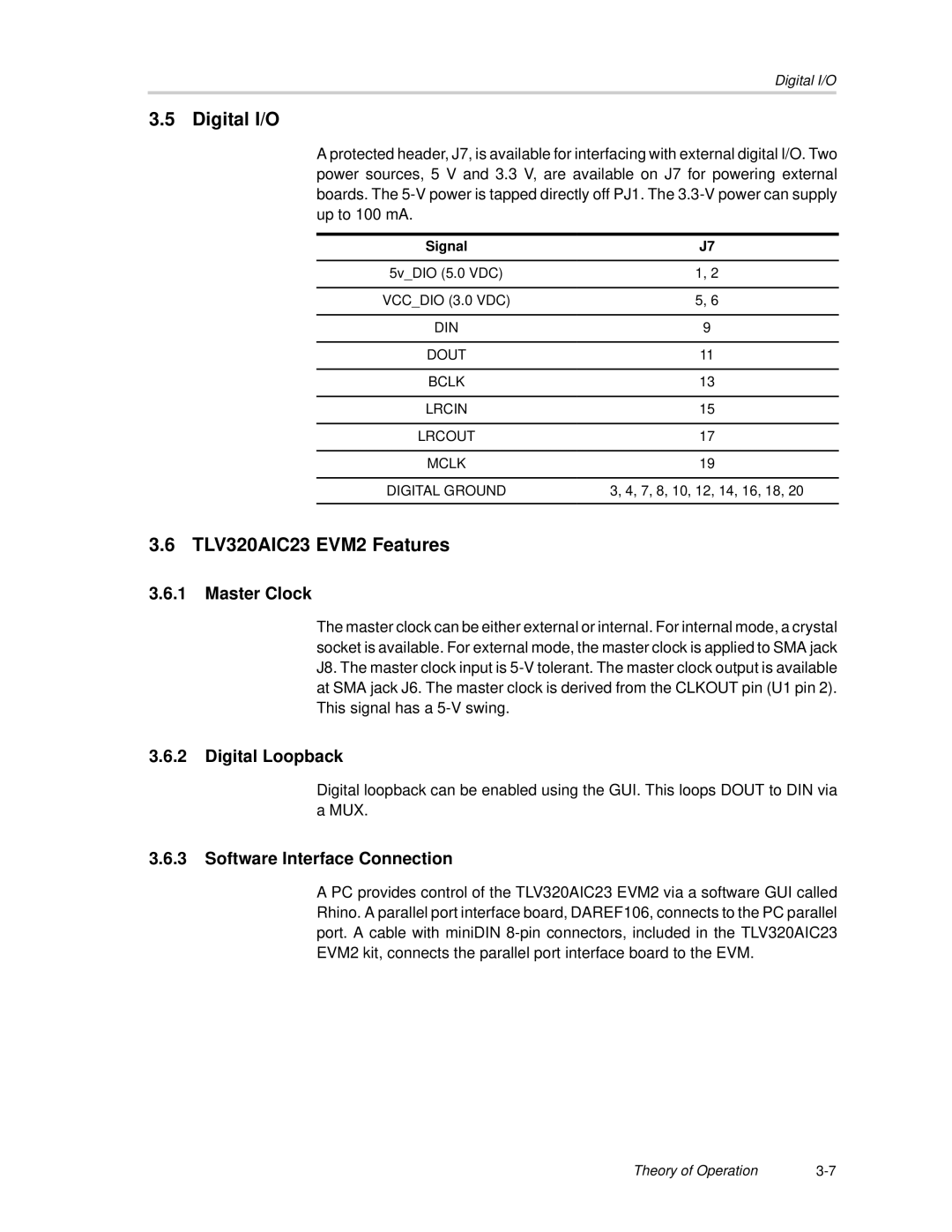

A protected header, J7, is available for interfacing with external digital I/O. Two power sources, 5 V and 3.3 V, are available on J7 for powering external boards. The

Signal | J7 |

|

|

5v_DIO (5.0 VDC) | 1, 2 |

|

|

VCC_DIO (3.0 VDC) | 5, 6 |

|

|

DIN | 9 |

|

|

DOUT | 11 |

|

|

BCLK | 13 |

|

|

LRCIN | 15 |

|

|

LRCOUT | 17 |

|

|

MCLK | 19 |

|

|

DIGITAL GROUND | 3, 4, 7, 8, 10, 12, 14, 16, 18, 20 |

|

|

3.6 TLV320AIC23 EVM2 Features

3.6.1Master Clock

The master clock can be either external or internal. For internal mode, a crystal socket is available. For external mode, the master clock is applied to SMA jack J8. The master clock input is

3.6.2Digital Loopback

Digital loopback can be enabled using the GUI. This loops DOUT to DIN via

aMUX.

3.6.3Software Interface Connection

A PC provides control of the TLV320AIC23 EVM2 via a software GUI called Rhino. A parallel port interface board, DAREF106, connects to the PC parallel port. A cable with miniDIN

Theory of Operation |