YMF724F

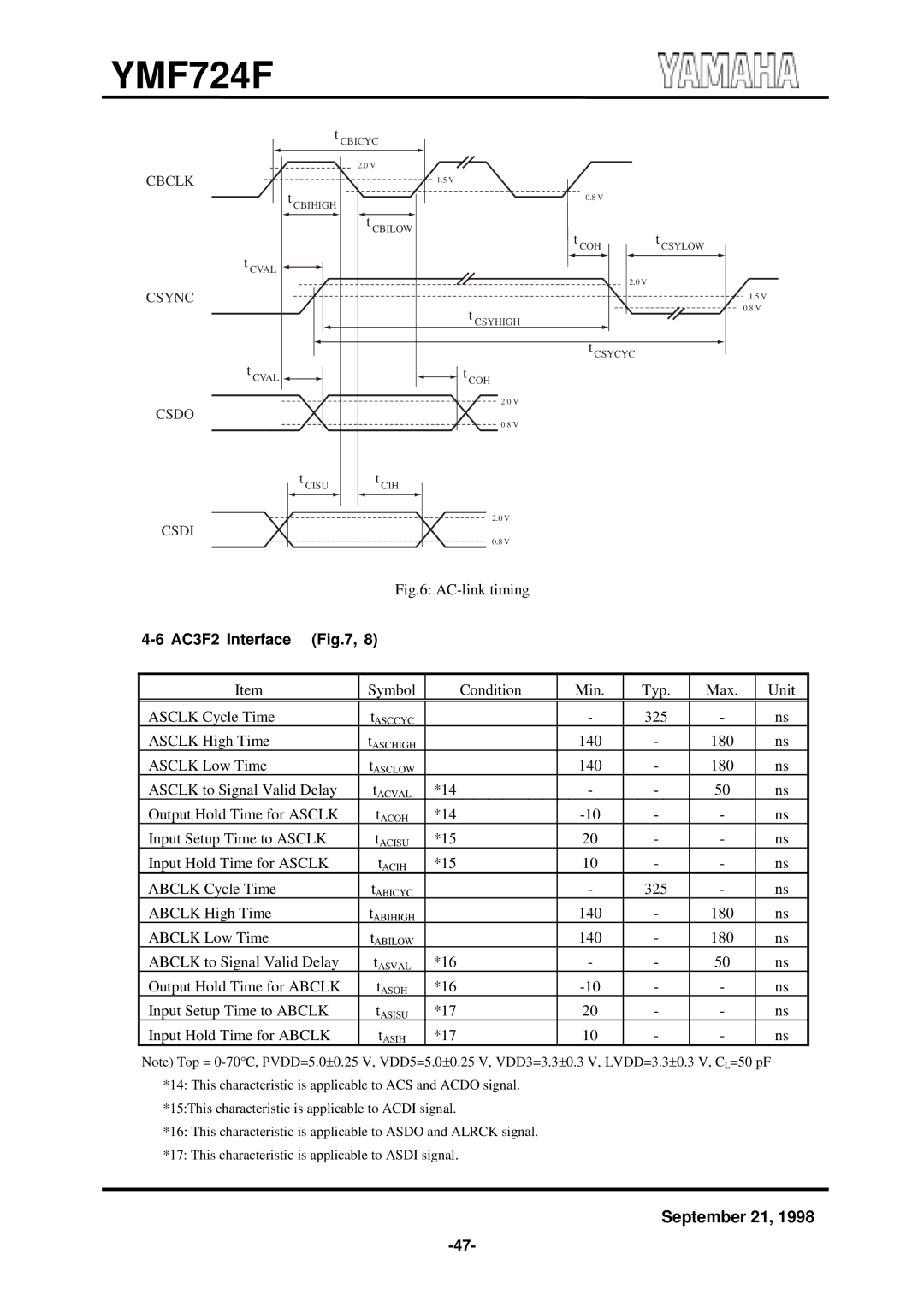

tCBICYC

| 2.0 V |

|

|

CBCLK | 1.5 V |

|

|

t CBIHIGH |

| 0.8 V |

|

|

|

| |

| t CBILOW | t COH | t CSYLOW |

|

| ||

t CVAL |

|

|

|

|

| 2.0 V |

|

CSYNC |

|

| 1.5 V |

|

| t CSYHIGH | 0.8 V |

|

|

| |

|

| t CSYCYC |

|

t CVAL | t | COH |

|

|

|

| |

|

| 2.0 V |

|

CSDO |

| 0.8 V |

|

|

|

| |

t CISU | t CIH |

|

|

|

| 2.0 V |

|

CSDI |

| 0.8 V |

|

|

|

|

Fig.6: AC-link timing

4-6 AC3F2 Interface (Fig.7, 8)

Item | Symbol | Condition | Min. | Typ. | Max. | Unit |

|

|

|

|

|

|

|

ASCLK Cycle Time | tASCCYC |

| - | 325 | - | ns |

ASCLK High Time | tASCHIGH |

| 140 | - | 180 | ns |

ASCLK Low Time | tASCLOW |

| 140 | - | 180 | ns |

ASCLK to Signal Valid Delay | tACVAL | *14 | - | - | 50 | ns |

Output Hold Time for ASCLK | tACOH | *14 | - | - | ns | |

Input Setup Time to ASCLK | tACISU | *15 | 20 | - | - | ns |

Input Hold Time for ASCLK | tACIH | *15 | 10 | - | - | ns |

ABCLK Cycle Time | tABICYC |

| - | 325 | - | ns |

ABCLK High Time | tABIHIGH |

| 140 | - | 180 | ns |

ABCLK Low Time | tABILOW |

| 140 | - | 180 | ns |

ABCLK to Signal Valid Delay | tASVAL | *16 | - | - | 50 | ns |

Output Hold Time for ABCLK | tASOH | *16 | - | - | ns | |

Input Setup Time to ABCLK | tASISU | *17 | 20 | - | - | ns |

Input Hold Time for ABCLK | tASIH | *17 | 10 | - | - | ns |

Note) Top =

*15:This characteristic is applicable to ACDI signal.

*16: This characteristic is applicable to ASDO and ALRCK signal.

*17: This characteristic is applicable to ASDI signal.

September 21, 1998