YMF724F

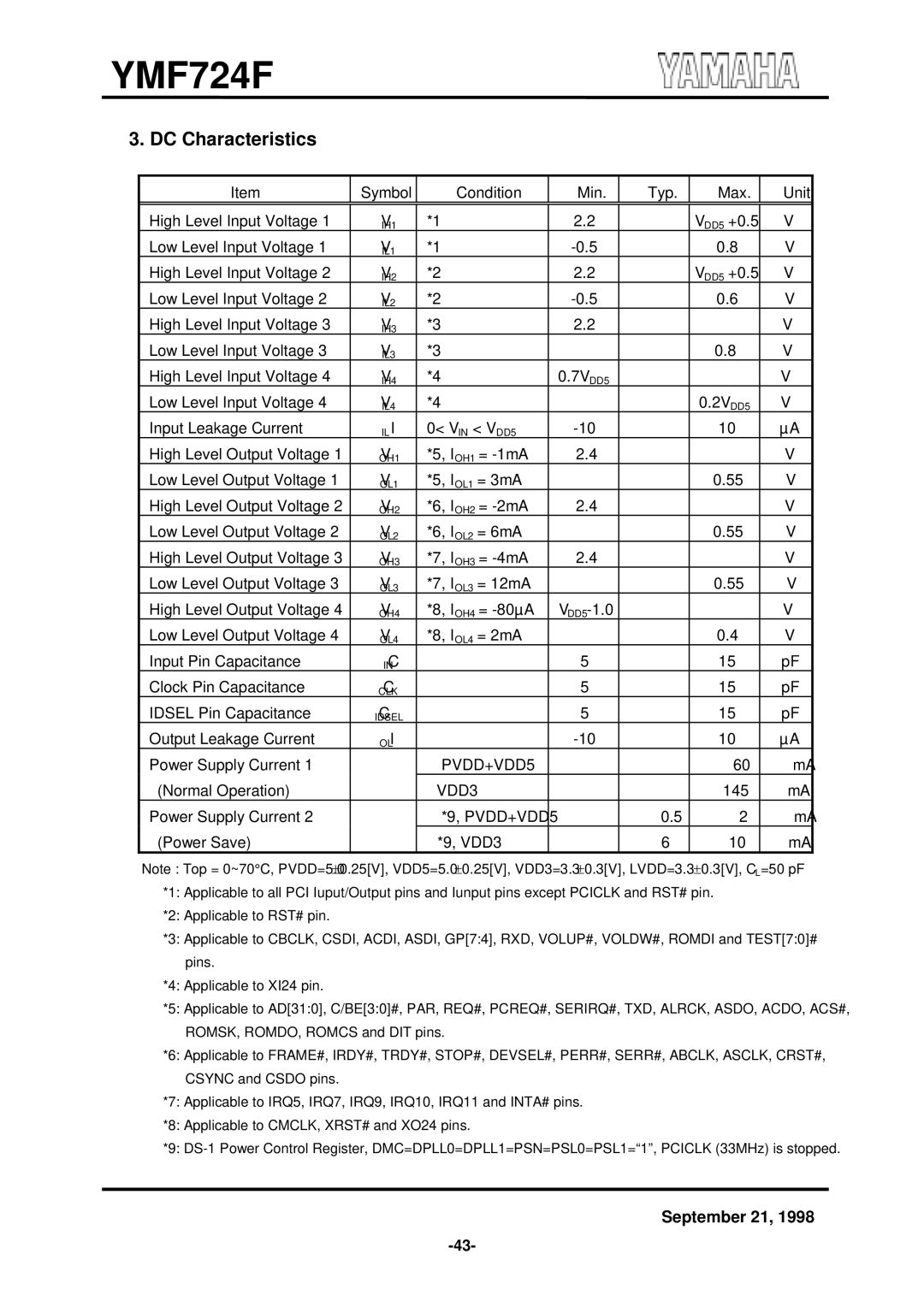

3. DC Characteristics

Item | Symbol | Condition | Min. | Typ. | Max. | Unit |

|

|

|

|

|

|

|

High Level Input Voltage 1 | VIH1 | *1 | 2.2 |

| VDD5 +0.5 | V |

Low Level Input Voltage 1 | VIL1 | *1 |

| 0.8 | V | |

High Level Input Voltage 2 | VIH2 | *2 | 2.2 |

| VDD5 +0.5 | V |

Low Level Input Voltage 2 | VIL2 | *2 |

| 0.6 | V | |

High Level Input Voltage 3 | VIH3 | *3 | 2.2 |

|

| V |

Low Level Input Voltage 3 | VIL3 | *3 |

|

| 0.8 | V |

High Level Input Voltage 4 | VIH4 | *4 | 0.7VDD5 |

|

| V |

Low Level Input Voltage 4 | VIL4 | *4 |

|

| 0.2VDD5 | V |

Input Leakage Current | IIL | 0< VIN < VDD5 |

| 10 | µA | |

High Level Output Voltage 1 | VOH1 | *5, IOH1 = | 2.4 |

|

| V |

Low Level Output Voltage 1 | VOL1 | *5, IOL1 = 3mA |

|

| 0.55 | V |

High Level Output Voltage 2 | VOH2 | *6, IOH2 = | 2.4 |

|

| V |

Low Level Output Voltage 2 | VOL2 | *6, IOL2 = 6mA |

|

| 0.55 | V |

High Level Output Voltage 3 | VOH3 | *7, IOH3 = | 2.4 |

|

| V |

Low Level Output Voltage 3 | VOL3 | *7, IOL3 = 12mA |

|

| 0.55 | V |

High Level Output Voltage 4 | VOH4 | *8, IOH4 = | V |

|

| V |

Low Level Output Voltage 4 | VOL4 | *8, IOL4 = 2mA |

|

| 0.4 | V |

Input Pin Capacitance | CIN |

| 5 |

| 15 | pF |

Clock Pin Capacitance | CCLK |

| 5 |

| 15 | pF |

IDSEL Pin Capacitance | CIDSEL |

| 5 |

| 15 | pF |

Output Leakage Current | IOL |

|

| 10 | µA | |

Power Supply Current 1 |

| PVDD+VDD5 |

|

| 60 | mA |

(Normal Operation) |

| VDD3 |

|

| 145 | mA |

Power Supply Current 2 |

| *9, PVDD+VDD5 |

| 0.5 | 2 | mA |

(Power Save) |

| *9, VDD3 |

| 6 | 10 | mA |

Note : Top = 0~70°C, PVDD=5.0 ±0.25[V], VDD5=5.0±0.25[V], VDD3=3.3±0.3[V], LVDD=3.3±0.3[V], CL=50 pF *1: Applicable to all PCI Iuput/Output pins and Iunput pins except PCICLK and RST# pin.

*2: Applicable to RST# pin.

*3: Applicable to CBCLK, CSDI, ACDI, ASDI, GP[7:4], RXD, VOLUP#, VOLDW#, ROMDI and TEST[7:0]# pins.

*4: Applicable to XI24 pin.

*5: Applicable to AD[31:0], C/BE[3:0]#, PAR, REQ#, PCREQ#, SERIRQ#, TXD, ALRCK, ASDO, ACDO, ACS#, ROMSK, ROMDO, ROMCS and DIT pins.

*6: Applicable to FRAME#, IRDY#, TRDY#, STOP#, DEVSEL#, PERR#, SERR#, ABCLK, ASCLK, CRST#, CSYNC and CSDO pins.

*7: Applicable to IRQ5, IRQ7, IRQ9, IRQ10, IRQ11 and INTA# pins.

*8: Applicable to CMCLK, XRST# and XO24 pins.

*9:

September 21, 1998