YMF724F

4. AC Characteristics

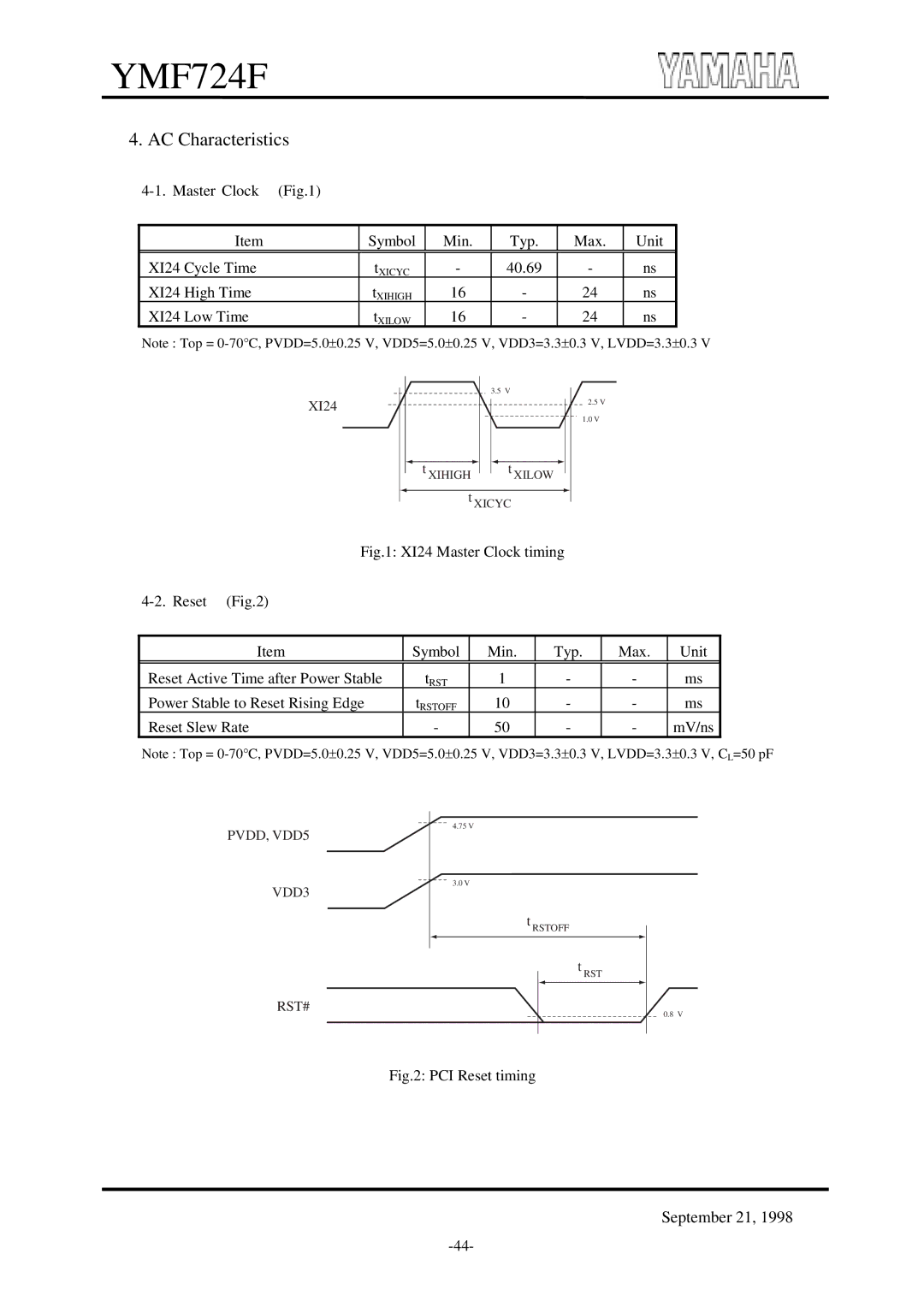

4-1. Master Clock (Fig.1)

Item

Symbol

Min.

Typ.

Max.

Unit

XI24 Cycle Time | tXICYC | - | 40.69 | - | ns |

XI24 High Time | tXIHIGH | 16 | - | 24 | ns |

XI24 Low Time | tXILOW | 16 | - | 24 | ns |

Note : Top =

|

| 3.5 V | ||

XI24 |

|

| 2.5 V | |

|

|

| ||

|

|

|

| 1.0 V |

|

|

|

|

|

t XIHIGH |

| t XILOW | ||

tXICYC

Fig.1: XI24 Master Clock timing

4-2. Reset (Fig.2)

Item | Symbol | Min. | Typ. | Max. | Unit |

|

|

|

|

|

|

Reset Active Time after Power Stable | tRST | 1 | - | - | ms |

Power Stable to Reset Rising Edge | tRSTOFF | 10 | - | - | ms |

Reset Slew Rate | - | 50 | - | - | mV/ns |

Note : Top =

4.75 V

PVDD, VDD5

3.0 V

VDD3

t RSTOFF

t RST

RST#

0.8 V

Fig.2: PCI Reset timing

September 21, 1998