AD9883A

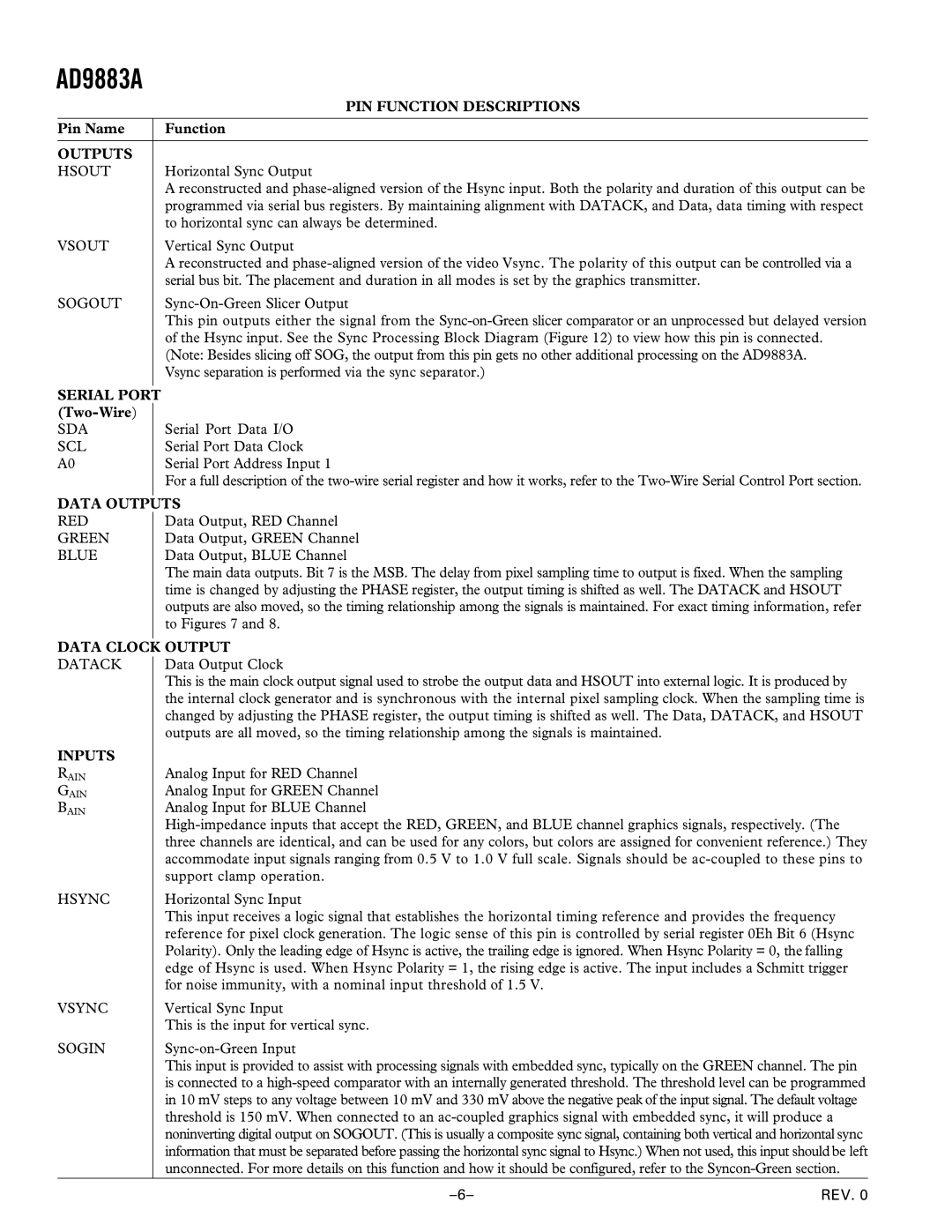

PIN FUNCTION DESCRIPTIONS

Pin Name |

|

| Function |

| |||

|

|

|

|

| |||

OUTPUTS |

|

|

|

| |||

HSOUT |

|

| Horizontal Sync Output |

| |||

|

|

|

|

|

| A reconstructed and | |

|

|

|

|

|

| programmed via serial bus registers. By maintaining alignment with DATACK, and Data, data timing with respect | |

|

|

|

|

|

| to horizontal sync can always be determined. |

|

VSOUT |

|

| Vertical Sync Output |

| |||

|

|

|

|

|

| A reconstructed and | |

|

|

|

|

|

| serial bus bit. The placement and duration in all modes is set by the graphics transmitter. |

|

SOGOUT |

|

|

|

| |||

|

|

|

|

|

| This pin outputs either the signal from the | |

|

|

|

|

|

| of the Hsync input. See the Sync Processing Block Diagram (Figure 12) to view how this pin is connected. | |

|

|

|

|

|

| (Note: Besides slicing off SOG, the output from this pin gets no other additional processing on the AD9883A. |

|

|

|

|

|

|

| Vsync separation is performed via the sync separator.) |

|

|

|

|

|

|

|

|

|

SERIAL POR | T |

|

| ||||

|

|

|

|

| |||

SDA |

|

| Serial Port Data I/O |

| |||

SCL |

|

| Serial Port Data Clock |

| |||

A0 |

|

| Serial Port Address Input 1 |

| |||

|

|

|

|

|

| For a full description of the | |

DATA OUTP |

|

|

| TS |

| ||

|

| U |

| ||||

RED |

|

| Data Output, RED Channel |

| |||

GREEN |

|

| Data Output, GREEN Channel |

| |||

BLUE |

|

| Data Output, BLUE Channel |

| |||

|

|

|

|

|

| The main data outputs. Bit 7 is the MSB. The delay from pixel sampling time to output is fixed. When the sampling | |

|

|

|

|

|

| time is changed by adjusting the PHASE register, the output timing is shifted as well. The DATACK and HSOUT | |

|

|

|

|

|

| outputs are also moved, so the timing relationship among the signals is maintained. For exact timing information, refer | |

|

|

|

|

|

| to Figures 7 and 8. |

|

DATA CLOC |

|

|

| OUTPUT |

| ||

K |

| ||||||

DATACK |

|

|

| Data Output Clock |

| ||

|

|

|

|

|

| This is the main clock output signal used to strobe the output data and HSOUT into external logic. It is produced by | |

|

|

|

|

|

| the internal clock generator and is synchronous with the internal pixel sampling clock. When the sampling time is | |

|

|

|

|

|

| changed by adjusting the PHASE register, the output timing is shifted as well. The Data, DATACK, and HSOUT | |

|

|

|

|

|

| outputs are all moved, so the timing relationship among the signals is maintained. |

|

INPUTS |

|

|

|

| |||

RAIN |

|

| Analog Input for RED Channel |

| |||

GAIN |

|

| Analog Input for GREEN Channel |

| |||

BAIN |

|

| Analog Input for BLUE Channel |

| |||

|

|

|

|

|

| ||

|

|

|

|

|

| three channels are identical, and can be used for any colors, but colors are assigned for convenient reference.) They | |

|

|

|

|

|

| accommodate input signals ranging from 0.5 V to 1.0 V full scale. Signals should be | |

|

|

|

|

|

| support clamp operation. |

|

HSYNC |

|

| Horizontal Sync Input |

| |||

|

|

|

|

|

| This input receives a logic signal that establishes the horizontal timing reference and provides the frequency | |

|

|

|

|

|

| reference for pixel clock generation. The logic sense of this pin is controlled by serial register 0Eh Bit 6 (Hsync | |

|

|

|

|

|

| Polarity). Only the leading edge of Hsync is active, the trailing edge is ignored. When Hsync Polarity = 0, the falling | |

|

|

|

|

|

| edge of Hsync is used. When Hsync Polarity = 1, the rising edge is active. The input includes a Schmitt trigger | |

|

|

|

|

|

| for noise immunity, with a nominal input threshold of 1.5 V. |

|

VSYNC |

|

| Vertical Sync Input |

| |||

|

|

|

|

|

| This is the input for vertical sync. |

|

SOGIN |

|

|

|

| |||

|

|

|

|

|

| This input is provided to assist with processing signals with embedded sync, typically on the GREEN channel. The pin | |

|

|

|

|

|

| is connected to a | |

|

|

|

|

|

| in 10 mV steps to any voltage between 10 mV and 330 mV above the negative peak of the input signal. The default voltage | |

|

|

|

|

|

| threshold is 150 mV. When connected to an | |

|

|

|

|

|

| noninverting digital output on SOGOUT. (This is usually a composite sync signal, containing both vertical and horizontal sync | |

|

|

|

|

|

| information that must be separated before passing the horizontal sync signal to Hsync.) When not used, this input should be left | |

|

|

|

|

|

| unconnected. For more details on this function and how it should be configured, refer to the | |

|

|

|

|

|

| REV. 0 | |