AD9883A

Table XXXIV. Detected Coast Input Polarity Status

Hsync Polarity Status | Result |

|

|

0 | Coast Polarity Negative |

1 | Coast Polarity Positive |

|

|

157 4:2:2 Output Mode Select

A bit that configures the output data in 4:2:2 mode. This mode can be used to reduce the number of data lines used from 24 down to 16 for applications using YUV, VCbCr, or PbPr graphics signals. A timing dia- gram for this mode is shown in Figure 9.

Recommended input and output configurations are shown in Table XXXV. In 4:2:2 mode, the red and blue channels can be interchanged to help satisfy board layout or timing requirements, but the green channel must be configured for Y.

Table XXXV. 4:2:2 Output Mode Select

Select | Output Mode |

|

|

0 | 4:4:4 |

1 | 4:2:2 |

|

|

Table XXXVI. 4:2:2 Input/Output Configuration

| Input |

|

Channel | Connection | Output Format |

|

|

|

Red | V | U/V |

Green | Y | Y |

Blue | U | High Impedance |

|

|

|

A

The

Data received or transmitted on the SDA line must be stable for the duration of the

There are five components to serial bus operation:

•Start Signal

•Slave Address Byte

•Base Register Address Byte

•Data Byte to Read or Write

•Stop Signal

When the serial interface is inactive (SCL and SDA are high) communications are initiated by sending a start signal. The start signal is a

The first eight bits of data transferred after a start signal com- prising a

Table XXXVII. Serial Port Addresses

Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 |

A6 | A5 | A4 | A3 | A2 | A1 | A0 |

(MSB) |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 | 0 | 0 | 1 | 1 | 0 | 0 |

1 | 0 | 0 | 1 | 1 | 0 | 1 |

|

|

|

|

|

|

|

Data Transfer via Serial Interface

For each byte of data read or written, the MSB is the first bit of the sequence.

If the AD9883A does not acknowledge the master device during a write sequence, the SDA remains high so the master can generate a stop signal. If the master device does not acknowledge the AD9883A during a read sequence, the AD9883A interprets this as “end of data.” The SDA remains high so the master can generate a stop signal.

Writing data to specific control registers of the AD9883A requires that the

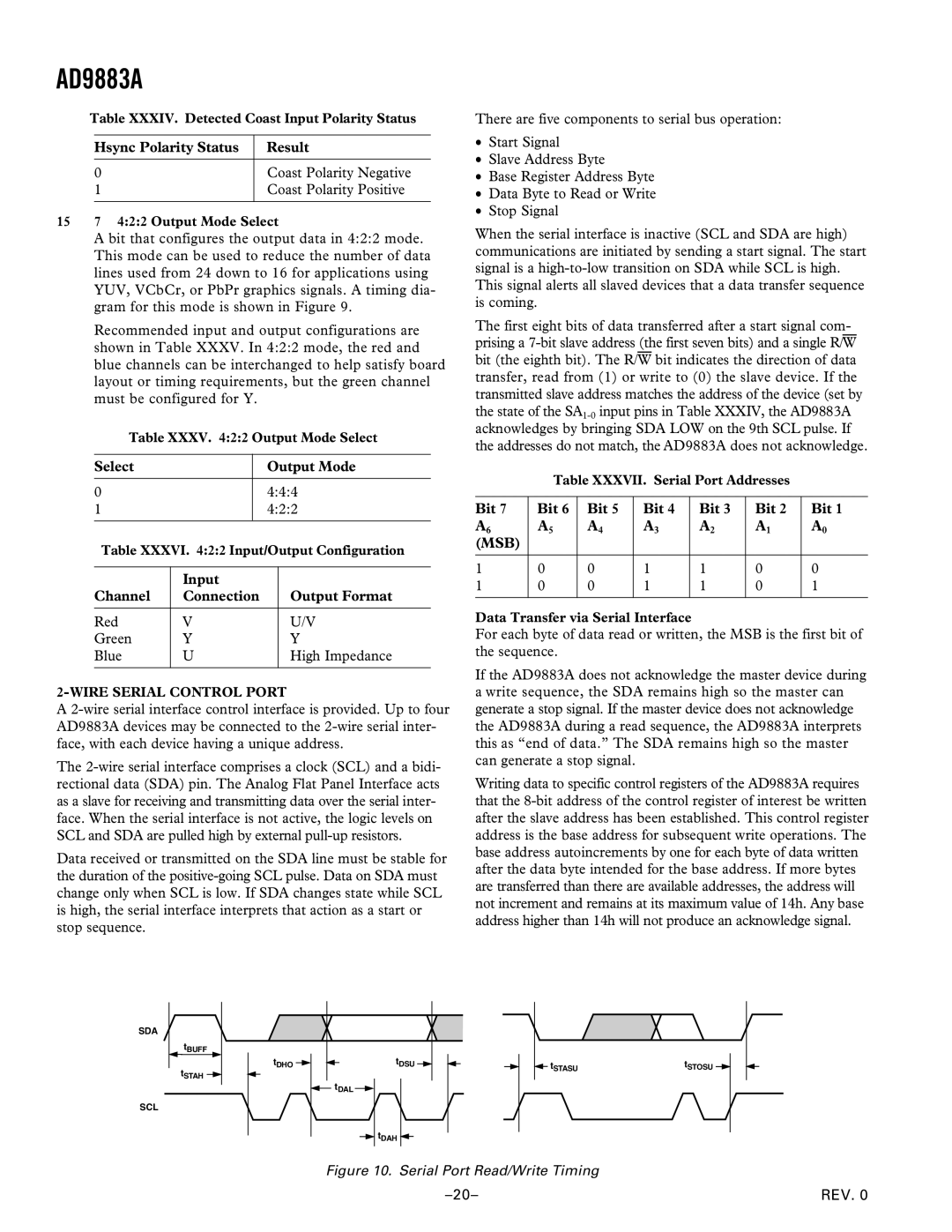

SDA

SCL

tBUFF

tSTAH ![]()

tDHO |

|

|

|

| tDSU |

|

| ||||

|

|

|

|

|

|

![]() tDAL

tDAL ![]()

![]() tDAH

tDAH ![]()

tSTASU | tSTOSU |

Figure 10. Serial Port Read/Write Timing

REV. 0 |