AD9883A

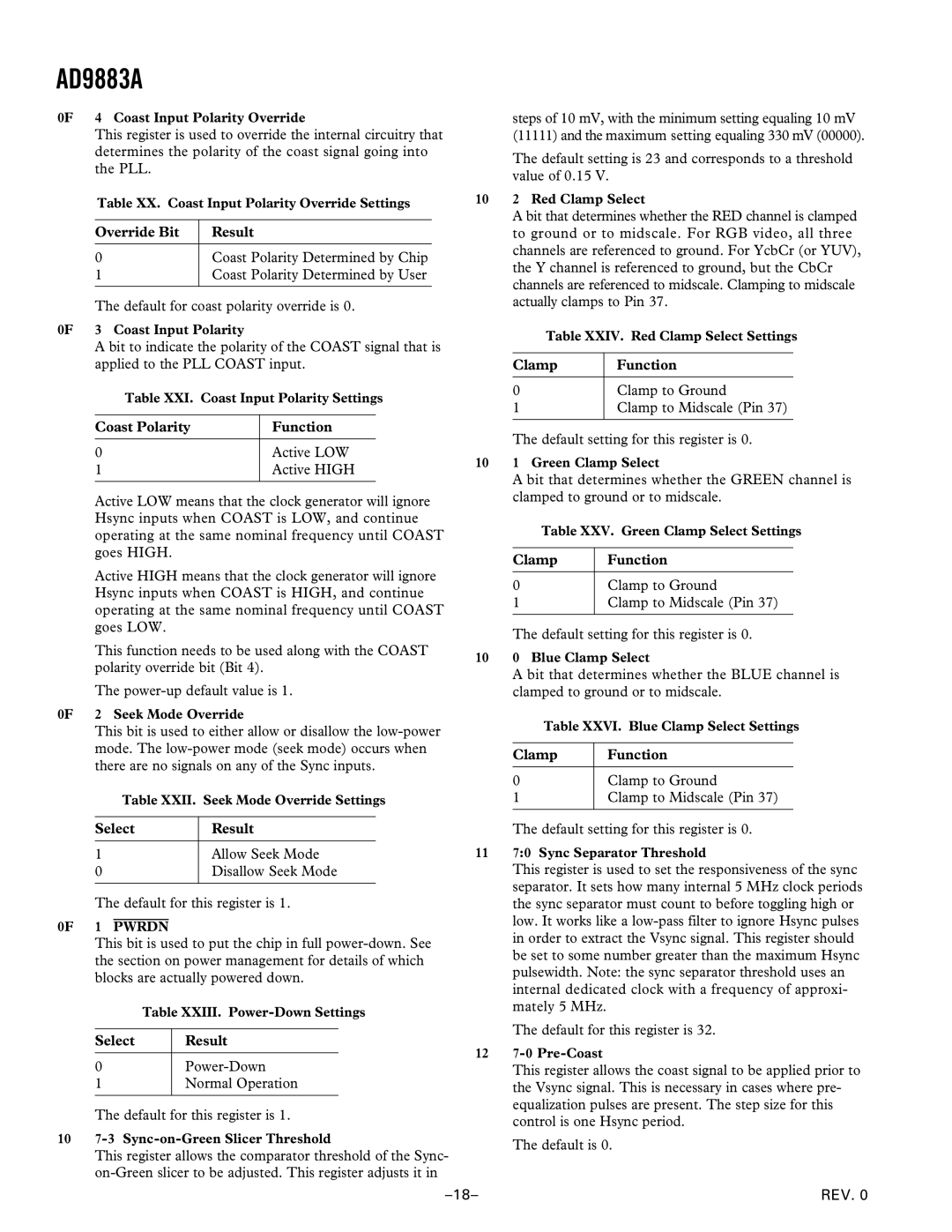

0F 4 Coast Input Polarity Override

This register is used to override the internal circuitry that determines the polarity of the coast signal going into the PLL.

Table XX. Coast Input Polarity Override Settings

Override Bit | Result |

|

|

0 | Coast Polarity Determined by Chip |

1 | Coast Polarity Determined by User |

|

|

The default for coast polarity override is 0.

0F 3 Coast Input Polarity

A bit to indicate the polarity of the COAST signal that is applied to the PLL COAST input.

Table XXI. Coast Input Polarity Settings

Coast Polarity | Function |

|

|

0 | Active LOW |

1 | Active HIGH |

|

|

Active LOW means that the clock generator will ignore Hsync inputs when COAST is LOW, and continue operating at the same nominal frequency until COAST goes HIGH.

Active HIGH means that the clock generator will ignore Hsync inputs when COAST is HIGH, and continue operating at the same nominal frequency until COAST goes LOW.

This function needs to be used along with the COAST polarity override bit (Bit 4).

The power-up default value is 1.

0F 2 Seek Mode Override

This bit is used to either allow or disallow the

Table XXII. Seek Mode Override Settings

Select | Result |

|

|

1 | Allow Seek Mode |

0 | Disallow Seek Mode |

|

|

The default for this register is 1.

0F 1 PWRDN

This bit is used to put the chip in full

Table XXIII.

Select | Result |

0Power-Down

1Normal Operation

The default for this register is 1.

107-3 Sync-on-Green Slicer Threshold

This register allows the comparator threshold of the Sync-

steps of 10 mV, with the minimum setting equaling 10 mV (11111) and the maximum setting equaling 330 mV (00000).

The default setting is 23 and corresponds to a threshold value of 0.15 V.

102 Red Clamp Select

A bit that determines whether the RED channel is clamped to ground or to midscale. For RGB video, all three channels are referenced to ground. For YcbCr (or YUV), the Y channel is referenced to ground, but the CbCr channels are referenced to midscale. Clamping to midscale actually clamps to Pin 37.

Table XXIV. Red Clamp Select Settings

Clamp | Function |

0Clamp to Ground

1Clamp to Midscale (Pin 37)

The default setting for this register is 0.

101 Green Clamp Select

A bit that determines whether the GREEN channel is clamped to ground or to midscale.

Table XXV. Green Clamp Select Settings

Clamp | Function |

0Clamp to Ground

1Clamp to Midscale (Pin 37)

The default setting for this register is 0.

100 Blue Clamp Select

A bit that determines whether the BLUE channel is clamped to ground or to midscale.

Table XXVI. Blue Clamp Select Settings

Clamp | Function |

0Clamp to Ground

1Clamp to Midscale (Pin 37)

The default setting for this register is 0.

117:0 Sync Separator Threshold

This register is used to set the responsiveness of the sync separator. It sets how many internal 5 MHz clock periods the sync separator must count to before toggling high or low. It works like a

The default for this register is 32.

12

This register allows the coast signal to be applied prior to the Vsync signal. This is necessary in cases where pre- equalization pulses are present. The step size for this control is one Hsync period.

The default is 0.

REV. 0 |