Schematic Diagrams

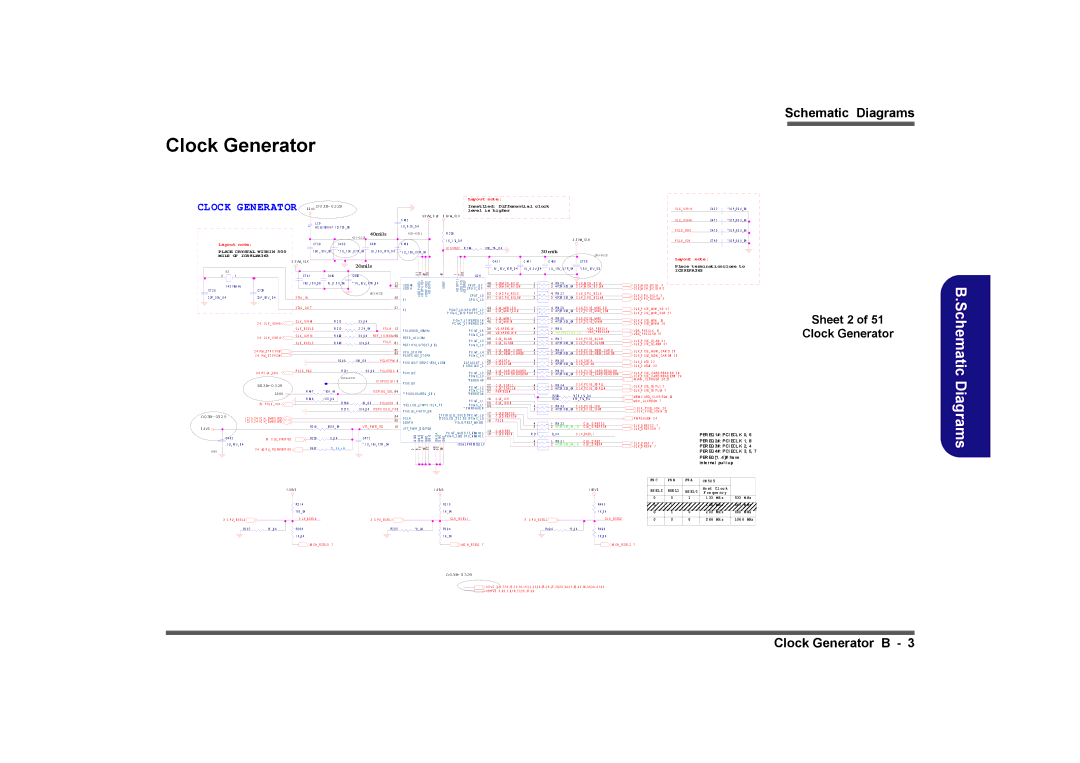

Clock Generator

Layout note:

CLOCK GENERATOR | 3. 3 V S |

|

|

|

|

|

|

|

|

|

|

| Insatlled: Differential clock |

|

|

|

|

|

|

| C L K _ I C H 1 4 | C 4 3 2 | *1 0 P _5 0 V _ 04 | |||||||||||

|

|

|

|

|

|

|

| C 46 2 |

| 3. 3 V M_ C LK | 3 . 3V | M_ C L K | level is higher |

|

|

|

|

|

|

|

|

|

| C L K _ I C H 4 8 | C 4 7 1 | *1 0 P _5 0 V _ 04 | ||||||||

|

|

|

| . | L 2 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| 1 U _ 6 . 3V _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

| H C B 1 60 8 K F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P C L K _ K B C | C 4 7 3 | *1 0 P _5 0 V _ 04 | |||||

|

|

|

|

|

|

|

|

| 40mi l s |

|

|

| R 2 00 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 K _ 1 %_ 0 4 |

|

|

|

|

|

|

|

| 3 . 3 V M_ C L K |

| P C L K _ I C H | C 7 4 3 | *1 0 P _5 0 V _ 04 | |||||

Layout note: |

| C 7 3 8 |

| C 4 3 0 |

| C 4 61 |

|

| C 43 9 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| I C S V R E F R 1 99 | 3 00 _ 1% _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

PLACE CRYSTAL WITHIN 500 |

| 1 0U _ 10 V _ 08 | *. 1 U _ 1 0V _X 7 R _ 04 | . 1U _1 0 V _ X7 R _ 0 4 |

|

|

|

|

|

| 30 mi ls |

|

|

|

|

|

|

|

| |||||||||||||||

| *. 1 U _ 1 0V _ X 7 R _ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

MILS | OF | ICS9LPR363 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Layout | note: |

| |

|

|

| 3 . 3 V M_ C L K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C 4 3 1 | C 44 1 |

| C | 46 0 |

|

| C 7 3 6 |

|

| |||||

|

|

|

|

|

|

|

| 20mi l s |

|

|

|

|

|

|

|

|

|

|

| . 1U _ 10 V _ X7 R _ 0 4 | 1 U _ 6 . 3 V _0 4 | . 1 | U _ 1 0V _ X 7 R _ 04 |

| *1 0 U _ 10 V _ 0 8 |

| Place terminationclose to | |||||||

X 2 | 1 |

|

| C 7 4 1 |

| C 4 40 | C 4 59 |

|

|

| 21 | 28 | 42 50 |

| 47 |

| 1 7 56 | U 2 4 |

|

|

|

|

|

|

|

|

|

|

|

| ICS9LPR363 |

| ||

2 |

|

|

|

|

|

|

|

|

|

|

|

| I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

1 4. 3 1 8M H z |

| 1 0U _1 0 V _0 8 | 1U _6 . 3 V _ 04 | *. 1 U _ 10 V _ X 7R _0 4 |

| 1 1 | V D D 48 |

|

|

|

|

| V D D P C V D D P C I V D D R E F | C P U T _ L1 F | 4 9 | C LK M C H _ B C LK |

| 1 |

| 4 | R N 2 8 |

| C L K _M C H _ B C LK | C L K _M C H _B C LK 5 |

|

| ||||||||

|

|

|

|

|

|

|

| 4 5 |

|

|

|

|

| 4 8 | C LK M C H _ B C LK # |

| 2 |

| 3 | 4 P 2R X 33 _ 04 | C L K _M C H _ B C LK # |

|

| |||||||||||

C 7 2 8 |

| C 7 29 |

|

|

|

|

|

|

|

|

| V D D A |

|

|

|

|

| C P U C _ L1 F |

|

|

|

|

|

|

|

|

|

|

| C L K _M C H _B C LK # 5 |

|

| ||

|

|

|

|

|

|

|

| VD DCPXEI VD DCXEPI VD DCXEPI V DUCDP |

| REVF |

|

| 5 2 | C LK C P U _ B C L K |

| 1 |

| 4 | R N 2 7 |

| C L K _C P U _ B C L K |

|

|

|

| |||||||||

2 2P _ 5 0V _ 0 4 |

| 22 P _ 50 V _ 0 4 | X TA L _ I N |

|

|

|

| 5 8 |

|

| C P U T _ L 0 |

|

|

| C L K _C P U _ B C L K 3 |

|

| |||||||||||||||||

|

|

|

|

|

|

| X 1 |

|

|

|

|

|

| C P U C _ L 0 | 5 1 | C LK C P U _ B C L K # |

| 2 |

| 3 | 4 P 2R X 33 _ 04 | C L K _C P U _ B C L K # | C L K _C P U _ B C L K # 3 |

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| X TA L _ OU T |

|

|

|

|

|

| 5 7 | X 2 |

|

|

|

|

| P C I e T _L 8 / C P U I TP T _ L 2 | 4 4 | C LK _ MI N I _3 G |

| 1 |

| 4 | R N 2 9 |

| C L K _P C I E _ MI N I _ 3 G | C L K _P C I E _ MI N I _ 3 G 2 7 |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 3 | C LK _ MI N I _3 G # |

| 2 |

| 3 | 4 P 2R X 33 _ 04 | C L K _P C I E _ MI N I _ 3 G# | C L K _P C I E _ MI N I _ 3 G# 2 7 |

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P C I e C _ L8 / C P U I T P C _ L 2 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| C L K _ I C H 48 |

|

| R 2 12 | 3 3 _0 4 |

|

|

|

|

|

|

|

|

| P C I e T _L 7 / P E R E Q 1 # | 4 1 | C LK _ MI N I |

| 1 |

| 4 | R N 3 0 |

| C L K _P C I E _ MI N I | C L K _P C I E _ MI N I 26 |

|

| |||||

|

| 2 4 C L K _ I C H 4 8 |

|

|

|

|

|

|

|

|

|

|

| 4 0 | C LK _ MI N I # |

| 2 |

| 3 | 4 P 2R X 33 _ 04 C L K _P C I E _ MI N I # |

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P C I eC _L 7 / P E R E Q 2 # |

|

|

|

|

|

|

|

|

|

|

| C L K _P C I E _ MI N I # 2 6 |

|

| |||

|

|

| C L K _ B S E L 0 |

|

| R 2 13 | 2 . 2 K _ 04 |

| F S L A 1 2 | F S L A / U S B _ 4 8M H z |

|

|

|

| P C I eT _ L 6 | 3 9 | V G A P E XC LK |

| 4 |

| 1 | R N 8 |

|

|

| V GA _ P E X C L K | V GA _ P E X C L K 15 |

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 8 | V G A P E XC LK # |

| 3 |

| 2 | *4 P 2 R X 3 3_ 0 4_ + U | V GA _ P E X C L K # |

|

|

| ||||||||

|

|

| C L K _ I C H 14 |

|

| R 4 99 | 3 3 _0 4 | R E F _ 1 4 . 31 8 M 6 0 |

|

|

|

|

|

|

| P C I e C _ L 6 |

|

|

| V GA _ P E X C L K # 1 5 |

|

|

| |||||||||||

|

| 2 4 C L K _ I C H 1 4 |

|

| R E F 0 _ 14 . 3 1 8M |

|

|

|

| 3 6 | C LK _ GL A N |

| 4 |

| 1 | R N 7 |

| C L K _P C I E _ GL A N |

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

| F S L C 6 1 |

|

|

|

| P C I eT _ L 5 |

|

|

| C L K _P C I E _ GL A N 3 1 |

|

| |||||||||||||

|

|

| C L K _ B S E L 2 |

|

| R 4 98 | 1 0 K _0 4 |

|

| R E F 1 / F S L C / T E S T _S E L |

|

|

| P C I e C _ L 5 | 3 5 | C LK _ GL A N # |

| 3 |

| 2 | 4 P 2R X 33 _ 04 | C L K _P C I E _ GL A N # | C L K _P C I E _ GL A N # 3 1 |

|

| |||||||||

|

| 2 4 P M _S T P C P U # |

|

|

|

|

|

|

|

| 6 2 | C P U _S T O P # |

|

|

|

|

| P C I eT _ L 4 | 3 0 | C LK _ N E W _ C A R D |

| 4 |

| 1 | R N 3 7 |

| C L K _P C I E _ N E W _ C A R D | C L K _P C I E _ N E W _ C A R D 2 6 |

|

| ||||

|

| 2 4 P M_ S T P P C I # |

|

|

|

|

|

|

|

| 6 3 |

|

|

|

|

| 3 1 | C LK _ N E W _ C A R D # | 3 |

| 2 | 4 P 2R X 33 _ 04 | C L K _P C I E _ N E W _ C A R D # | C L K _P C I E _ N E W _ C A R D # 2 6 |

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| P C I / P C I E X _S T OP # |

|

|

|

| P C I e C _ L 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| R 2 0 8 | 1 0K _ 0 4 |

| P C L K T P M 5 | P C I C LK 3 / * S E LP C I E X 0_ L C D # | S A T A C L K T _ L | 2 6 | C LK S A T A |

| 4 |

| 1 | R N 3 6 |

| C L K _S A T A | C L K _S A TA 2 2 |

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| 2 7 | C LK S A T A # |

| 3 |

| 2 | 4 P 2R X 33 _ 04 C L K _S A T A # | C L K _S A TA # 2 2 |

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| S A TA C LK C _ L |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| 3 4 P C LK _K B C | P C L K _ K B C |

|

| R 22 1 | 3 3 _0 4 | P C L K K B C 4 | P C I C LK 2 |

|

|

|

|

|

| P C I eT _ L 3 | 2 4 | C LK _ C A R D R E A D E R | 4 |

| 1 | R N 3 5 |

| C L K _P C I E _ C A R D R E A D E R | C L K _P C I E _ C A R D R E A D E R 2 9 |

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 5 | C LK _ C A R D R E A D E R # | 3 |

| 2 | 4 P 2R X 33 _ 04 C L K _P C I E _ C A R D R E A D E R # |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P C I e C _ L 3 | 3 3 |

|

|

|

|

|

|

|

|

|

| C L K _P C I E _ C A R D R E A D E R # 2 9 |

|

| |||

|

|

|

|

|

|

| I C S P C I C LK 1 3 |

|

|

|

|

|

|

| *P E R E Q 4 # |

|

|

|

|

|

|

|

|

|

| W LA N _ C L K R E Q# | 2 6 , 27 |

|

| |||||

|

|

|

|

|

|

|

| P C I C LK 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| C L K _P C I E _ 3G P LL |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 2 | C LK _ 3 GP L L |

| 4 |

| 1 | R N 3 4 |

| C L K _P C I E _ 3G P L L | 7 |

|

| |||||

|

|

| R 49 7 |

| * 10 K _ 04 |

| I C S R E Q_ S E L 6 4 |

|

|

|

|

|

|

| P C I eT _ L 2 | 2 3 | C LK _ 3 GP L L # |

| 3 |

| 2 | 4 P 2R X 33 _ 04 | C L K _P C I E _ 3G P LL # |

|

| |||||||||

|

| 3. 3 V S |

|

|

| ** P C I C L K 0 / R E Q _S E L |

|

|

| P C I e C _ L 2 | 3 2 | P E R E Q3 # |

|

|

|

|

|

|

|

|

| C L K _P C I E _ 3G P L L# 7 |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| *P E R E Q 3 # |

|

|

|

|

| R 2 09 | *4 7 5 _1 % _0 4 | N E W C A R D _ C L K R E Q# 26 |

|

| ||||||||||

|

|

|

| R 60 6 |

| 1 0 K _0 4 |

|

|

|

|

|

|

|

|

|

|

|

| 1 9 | C LK _ I C H |

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P C I eT _ L 1 |

|

|

| R 2 03 | 4 75 _ 1 %_ 0 4 | MC H _ C L K R E Q# 7 |

|

|

| |||||||||

|

| 23 P C L K _ I C H |

|

|

|

| R 50 9 | 33 _ 0 4 | P C L K I C H 9 |

|

|

|

|

|

|

| 2 0 | C LK _ I C H # |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| *S E L L C D _2 7 #/ P C I C L K _ F 5 |

|

| P C I e C _ L 1 |

| 4 |

| 1 | R N 3 3 |

| C L K _P C I E _ I C H |

|

|

|

| ||||||||||||||

|

|

|

|

|

|

| R 21 5 | 1 0 K _0 4 I C S P C I C L K _ F 4 8 |

|

| 3 4 |

|

|

|

| C L K _ P C I E _ I C H 2 3 |

|

| ||||||||||||||||

|

|

|

|

|

|

| P C I C LK _ F 4 / I T P _E N |

|

|

| * P W R S A V E # |

|

|

| 3 |

| 2 | 4 P 2R X 33 _ 04 C L K _P C I E _ I C H # |

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 7 | C LK D R E F S S |

|

|

|

|

|

|

|

|

| C L K _ P C I E _ I C H # 23 |

|

| ||||

| 1 2, 1 3 , 2 4 I C H _ S MB C LK 0 |

|

|

|

|

|

|

|

| 5 4 | S C L K |

|

|

| 2 7 F I X/ LC D _ S S C G T/ P C I eT _ L 0 | 1 8 | C LK D R E F S S # |

|

|

|

|

|

|

|

|

| P W R S A V E # 2 4 |

|

|

| ||||

|

|

|

|

|

|

|

|

| 5 5 |

|

|

| 27 S S / L C D _S S C GC / P C I e C _ L 0 | 1 6 | F S L B |

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

| 1 2, 1 3 , 2 4 I C H _ S MB D A T0 |

|

|

|

|

|

|

|

| S D A T A |

|

|

|

|

| F S L B / T E S T_ MO D E |

| 4 |

| 1 | R N 3 2 |

|

|

| C LK _ D R E F S S |

|

|

|

| ||||

3 . 3 V S |

|

|

| R 2 19 | 10 0 K _ 04 | V TT _ P W R _ GD | 1 0 | V T T_ P W R _G D / P D # |

|

|

|

|

|

|

|

| 3 |

| 2 | 4 P 2R X 33 _ 04 _ |

| C LK _ D R E F S S # | C L K _D R E F S S 7 |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 4 | C LK D R E F |

|

|

|

|

|

|

|

|

| C L K _D R E F S S # 7 |

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A |

| P C I eT _ L9 / D O T T_ 9 6M H z L | 1 5 | C LK D R E F # | R 21 1 |

| 0_ 0 4 |

| C L K _B S E L 1 |

|

| PER EQ 1#: PCI ECLK 0, 6 | |||||||

C 4 4 2 | 24 C LK _ P W R GD |

| R 2 20 | 0 _0 4 | C 4 7 2 |

|

| ND N D ND ND N D | N D ND ND | P C I e C _ L 9/ D OT C _ 9 6M H z L |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

| *. 1 U _ 1 0V _ X 7R _ 04 | G G G G G | G G G |

| I C S 9 L P R 3 63 D G L F |

|

|

| 4 |

| 1 | R N 3 1 |

|

|

| C LK _ D R E F | C L K _D R E F 7 |

| PER EQ 2#: PCI ECLK 1, 8 | |||||||||

. 1 U _ 16 V _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 |

| 2 | 4 P 2R X 33 _ 04 _ |

| C LK _ D R E F # |

| PER EQ 3#: PCI ECLK 2, 4 | ||||||||||||

|

| 2 4 dG P U _ R U N P W R OK |

| R 6 07 | *0 _ 0 4_ + H |

|

|

|

| 2 6 1 3 29 3 7 | 4 6 5 3 | 59 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| C L K _D R E F # 7 |

| ||||||

EMI |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PER EQ 4#: PCI ECLK 3, 5, 7 | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Sheet 2 of 51

Clock Generator

![]() B.Schematic Diagrams

B.Schematic Diagrams

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PER EQ [1. .4 ]# ha ve |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| inte rna l pul l up |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| FS C | FS B | FS A | CK 50 5 |

|

|

|

|

|

|

|

|

|

|

|

|

| 1 . 0 5V S |

|

|

|

|

|

|

|

|

|

|

| 1 . 0 5V S |

|

|

|

|

|

|

|

| 1 . 05 V S | BS EL 2 | BSE L1 | BS EL 0 | Ho st | Cl oc k |

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| F re que nc y |

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 0 | 1 | 1 33 | MH z |

| 533 | M Hz |

|

|

|

|

|

|

|

|

|

| R 2 1 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| R 2 1 0 |

|

|

|

|

|

|

|

|

| R 4 9 5 | 0 | 1 | 1 | 1 66 | MH z |

| 667 | M Hz | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| *5 6 _ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 K _ 04 |

|

|

|

|

|

|

|

|

| 1 K _0 4 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 1 | 0 | 2 00 | MH z |

| 800 | M Hz | ||||||||||

|

|

|

|

|

|

|

|

|

|

| C L K _B S E L 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C L K _ B S E L 1 |

|

|

|

|

|

|

|

|

|

| C L K _ B S E L2 |

|

|

|

|

|

|

|

| |||

3 C P U _ B S E L 0 |

|

|

|

|

|

| 3 C P U _ B S E L 1 |

|

|

|

|

|

|

|

|

|

|

| 3 C P U _ B S E L 2 |

|

|

|

| 0 | 0 | 0 | 2 66 | MH z |

| 106 6 | MHz | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

| R 2 0 7 |

|

| 1K _0 4 |

| R 2 0 6 |

|

| R 2 0 5 | *0 _ 04 |

|

|

|

|

| R 2 0 4 |

|

|

| R 4 9 4 | *0 _0 4 |

| R 4 9 6 |

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

| 1 K _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 K _ 04 |

|

|

|

|

|

|

|

|

| 1 K _0 4 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| M C H _ B S E L 0 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MC H _ B S E L1 7 |

|

|

|

|

|

|

|

|

|

| M C H _ B S E L 2 7 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

3. 3 V S 3 , 6 , 7, 1 0 , 12 , 1 3 , 14 , 1 5, 2 2 , 2 3, 2 4 , 25 , 2 6 , 27 , 2 8, 2 9 , 3 0, 3 1 , 32 , 3 3 , 34 , 3 5, 3 9 , 4 1, 4 3

1. 0 5 V S 3 , 4, 5 , 7 , 9, 1 0 , 2 2, 2 5 , 37 , 3 9

Clock Generator B - 3