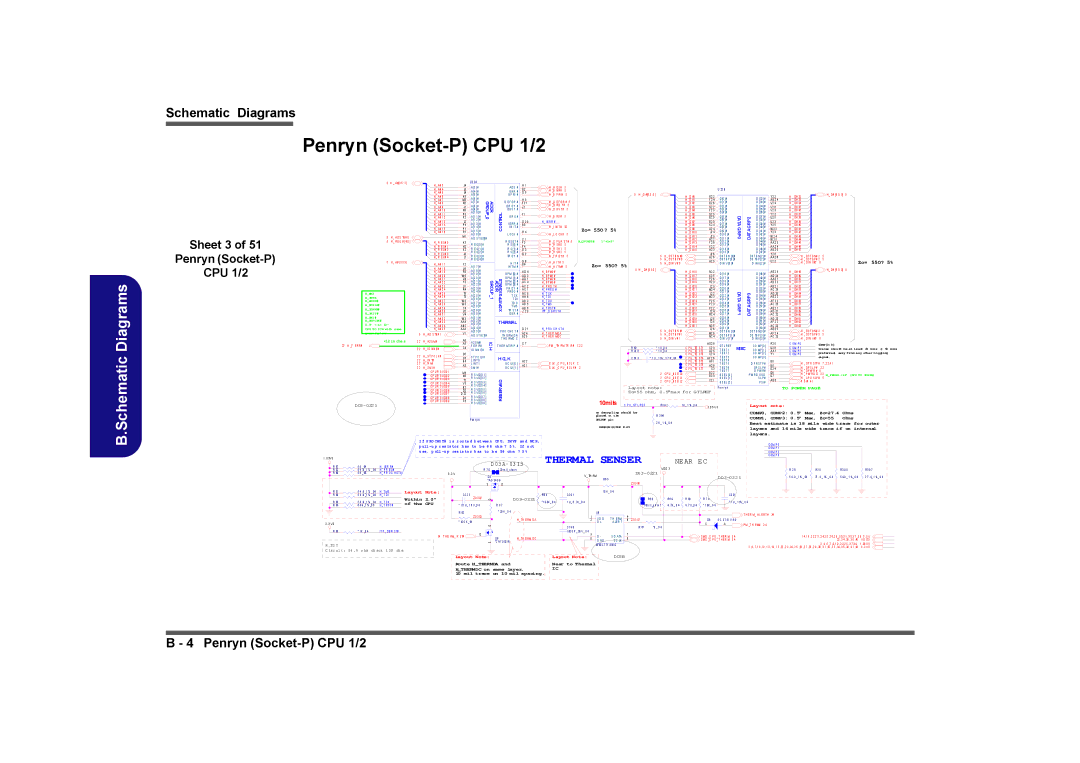

Schematic Diagrams

Penryn (Socket-P) CPU 1/2

B.Schematic Diagrams

Sheet 3 of 51

Penryn (Socket-P)

CPU 1/2

|

|

| 5 H _ A #[ 3 5 : 3 ] |

|

| H _ A # | 3 | J4 | U 2 2A |

|

|

|

| H 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| A [ 3 ] # |

|

|

| A D S # | H _A D S # 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| H _ A # 4 | L5 | A [ 4 ] # |

|

|

| B N R # | E 2 | H _B N R # 5 |

|

|

|

|

|

|

|

|

|

|

|

| U 22 B |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| H _ A # 5 | L4 |

|

|

| G 5 | H _B P R I # 5 |

|

|

|

|

| 5 | H _D #[ 6 3 : 0 ] |

|

|

|

|

|

|

|

|

|

|

|

|

| H _ D # [ 6 3: 0] 5 |

|

|

|

| ||||||

|

|

|

|

|

|

| H _ A # 6 | K 5 | A [ 5 ] # |

|

|

| B P R I # |

|

|

|

|

|

|

| H _D #0 |

| E 2 2 |

|

|

|

|

| Y 2 2 | H _ D # 32 |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

| H _ A # 7 | M3 | A [ 6 ] # | GROUP0 |

| D E F E R # | H 5 | H _D E F E R # 5 |

|

|

|

|

|

|

|

| H _D #1 |

| F 2 4 | D [ 0 ] # |

|

| D [ 32 ] # | A B 2 4 | H _ D # 33 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| H _ A # 8 | N 2 | A [ 7 ] # |

| F 2 1 |

|

|

|

|

|

|

|

| H _D #2 |

| E 2 6 | D [ 1 ] # |

|

| D [ 33 ] # | V 2 4 | H _ D # 34 |

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

| H _ A # 1 2 | P 2 | A [ 1 1 ] # | CONTROL | B R 0 # | C 1 | H _B R 0 # | 5 |

|

|

|

|

|

|

|

|

| H _D #6 |

| E 2 5 | D [ 5 ] # | DATAGRP0 | DATAGRP2 | D [ 37 ] # | U 2 5 | H _ D # 38 |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| A D S T B [ 0] # | RADD |

| H _D R D Y # | 5 |

|

|

|

|

|

|

|

| H _D #1 2 |

| H 2 2 | D [ 1 1 ] # | D [ 43 ] # | W 2 5 | H _ D # 44 |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

| H _ A # 9 | J1 | A [ 8 ] # |

|

|

| D R D Y # | E 1 | H _D B S Y # 5 |

|

|

|

|

|

|

|

| H _D #3 |

| G2 2 | D [ 2 ] # |

|

| D [ 34 ] # | V 2 6 | H _ D # 35 |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

| H _ A # 1 0 | N 3 | A [ 9 ] # |

|

|

| D B S Y # |

|

|

|

|

|

|

|

|

| H _D #4 |

| F 2 3 | D [ 3 ] # |

|

| D [ 35 ] # | V 2 3 | H _ D # 36 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| H _ A # 1 1 | P 5 | A [ 1 0 ] # |

|

|

|

| F 1 |

|

|

|

|

|

|

|

|

|

|

| H _D #5 |

| G2 5 | D [ 4 ] # |

|

| D [ 36 ] # | T 2 2 | H _ D # 37 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| H _ A # 1 3 | L2 | A [ 1 2 ] # |

|

|

|

| D 2 0 | H _ I E R R # |

|

|

|

|

|

|

|

|

|

| H _D #7 |

| E 2 3 | D [ 6 ] # |

|

| D [ 38 ] # | U 2 3 | H _ D # 39 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| H _ A # 1 4 | P 4 | A [ 1 3 ] # |

|

|

| I E R R # | B 3 | H _I N I T # 22 |

|

|

|

|

|

|

|

|

| H _D #8 |

| K 2 4 | D [ 7 ] # |

|

| D [ 39 ] # | Y 2 5 | H _ D # 40 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| H _ A # 1 5 | P 1 | A [ 1 4 ] # |

|

|

| I N I T # |

|

|

| Zo= 55O ? 5% |

|

|

|

|

| H _D #9 |

| G2 4 | D [ 8 ] # |

|

| D [ 40 ] # | W 2 2 | H _ D # 41 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| H _ A # 1 6 | R 1 | A [ 1 6 ] # |

|

|

| L OC K # | H 4 | H _L O C K # | 5 |

|

|

|

|

|

| H _D #1 0 |

| J2 4 | D [ 1 0 ] # |

|

| D [ 42 ] # | Y 2 3 | H _ D # 42 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| A [ 1 5 ] # |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D [ 9 ] # |

|

| D [ 41 ] # |

|

|

|

|

|

|

|

|

|

| |

|

|

| 5 H _ A D S TB # 0 |

|

|

|

| M1 |

|

|

|

|

|

|

|

|

|

| H_CPURST# | 1"<L<5" |

|

|

|

|

| H _D #1 1 |

| J2 3 |

|

|

|

|

| W 2 4 | H _ D # 43 |

|

|

|

|

|

|

|

| |

|

|

| 5 | H _ R E Q # [ 4: 0 ] |

|

| H _ R E Q# 0 | K 3 | R E Q[ 0 ] # |

|

|

| R E S E T # | F 3 | H _C P U R S T # | 5 |

|

|

|

|

| H _D #1 3 |

| F 2 6 | D [ 1 2 ] # |

|

| D [ 44 ] # | A A 2 3 | H _ D # 45 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

| H _ R E Q# 1 | H 2 |

|

|

| R S [ 0] # | F 4 | H _R S # 0 5 |

|

|

|

|

|

|

|

|

| H _D #1 4 |

| K 2 2 | D [ 1 3 ] # |

|

| D [ 45 ] # | A A 2 4 | H _ D # 46 |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

| H _ R E Q# 2 | K 2 | R E Q[ 1 ] # |

|

|

| R S [ 1] # | G 3 | H _R S # 1 5 |

|

|

|

|

|

|

|

|

| H _D #1 5 |

| H 2 3 | D [ 1 4 ] # |

|

| D [ 46 ] # | A B 2 5 | H _ D # 47 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| H _ R E Q# 3 | J3 | R E Q[ 2 ] # |

|

|

| R S [ 2] # | G 2 | H _R S # 2 5 |

|

|

|

|

|

|

|

|

|

|

| J2 6 | D [ 1 5 ] # |

|

| D [ 47 ] # | Y 2 6 |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| H _ R E Q# 4 | L1 | R E Q[ 3 ] # |

|

|

| TR D Y # |

| H _T R D Y # 5 |

|

|

|

|

|

| 5 H _ D S T B N #0 |

| H 2 6 | D S T B N [ 0] # |

| D S T B N [ 2 ] # | A A 2 6 | H _ D S T B N # 2 5 |

|

|

|

|

|

| |||||||||

|

|

| 5 H _ A # [ 3 5: 3 ] |

|

|

|

|

| R E Q[ 4 ] # |

|

|

|

| G 6 | H _H I T # 5 |

|

|

|

|

|

|

|

| 5 H _ D S T B P # 0 |

| H 2 5 | D S T B P [ 0 ] # |

| D S TB P [ 2 ] # | U 2 2 | H _ D S T B P # 2 5 |

| Zo= | 55O? 5% | ||||||||||

|

|

|

|

| H _ A # 1 7 | Y 2 |

|

|

|

| H I T # |

|

|

| Zo= | 55O? 5% |

|

| 5 | H _ D I N V # 0 |

|

| D I N V [ 0 ] # |

|

| D I N V [ 2 ] # | H _ D I N V #2 5 |

|

| |||||||||||||||

|

|

|

|

|

|

| A [ 1 7 ] # |

|

|

| E 4 | H _H I T M# | 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

| H _ A # 1 8 | U 5 |

|

|

| H I T M # | A D 4 |

|

| 5 | H _ D # [ 6 3: 0 ] |

| H _D #1 6 |

| N 2 2 |

|

|

|

|

| A E 2 4 | H _ D # 48 |

|

| H _ D # [ 6 3: | 0] 5 |

|

|

|

| ||||||||

|

|

|

|

|

|

| H _ A # 1 9 | R 3 | A [ 1 8 ] # |

|

|

| B P M [ 0] # | H _ B P M0 # |

|

|

|

|

|

|

|

|

|

|

| D [ 1 6 ] # |

|

| D [ 48 ] # |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

| H _ A # 2 0 | W 6 | A [ 1 9 ] # |

|

|

| A D 3 | H _ B P M1 # |

|

|

|

|

|

|

|

|

|

| H _D #1 7 |

| K 2 5 |

|

| A D 24 | H _ D # 49 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

| A [ 2 0 ] # |

|

|

| B P M [ 1] # |

|

|

|

|

|

|

|

|

|

|

| D [ 1 7 ] # |

|

| D [ 49 ] # |

|

|

|

|

|

|

|

| ||||||||||

|

| H_INIT# |

|

|

|

| H _ A # 2 1 | U 4 |

| GROUP 1 | XDP/ITPSIGNALS | A D 1 | H _ B P M2 # |

|

|

|

|

|

|

|

|

|

| H _D #1 8 |

| P 2 6 | DATAGRP1 | DATAGRP3 | A A 2 1 | H _ D # 50 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| H _ A # 3 1 | V 4 | A [ 3 0 ] # |

| D B R # | A C 4 | H _ B P M3 # |

|

|

|

|

|

|

|

|

|

| H _D #2 8 |

| R 2 4 | D [ 2 7 ] # | D [ 59 ] # | A C 22 | H _ D # 60 |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

| H _ A # 2 2 | Y 5 | A [ 2 1 ] # |

|

| A DDR | B P M [ 2] # |

|

|

|

|

|

|

|

|

|

| H _D #1 9 |

| R 2 3 | D [ 1 8 ] # |

|

| D [ 50 ] # | A B 2 2 | H _ D # 51 |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

| H _ A # 2 4 | R 4 | A [ 2 2 ] # |

|

| B P M [ 3] # | A C 1 | H _ P R E Q # |

|

|

|

|

|

|

|

|

|

| H _D #2 1 |

| M2 4 | D [ 1 9 ] # |

|

| D [ 51 ] # | A C 26 | H _ D # 53 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| A [ 2 3 ] # |

|

| P R D Y # |

|

|

|

|

|

|

|

|

|

|

| D [ 2 0 ] # |

|

| D [ 52 ] # |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

| H _ A # 2 3 | U 1 |

|

|

|

|

| A C 2 | H _ P R D Y # |

|

|

|

|

|

|

|

|

|

| H _D #2 0 |

| L2 3 |

|

|

|

|

| A B 2 1 | H _ D # 52 |

|

|

|

|

|

|

|

| |

|

| H_NMI |

|

|

|

| H _ A # 2 5 | T5 | A [ 2 4 ] # |

|

|

| P R E Q # | A C 5 | H _ T C K |

|

|

|

|

|

|

|

|

|

| H _D #2 2 |

| L2 2 | D [ 2 1 ] # |

|

| D [ 53 ] # | A D 20 | H _ D # 54 |

|

|

|

|

|

|

|

| ||

|

| H_INTR |

|

|

|

| H _ A # 2 6 | T3 | A [ 2 5 ] # |

|

|

| T C K | A A 6 | H _ T D I |

|

|

|

|

|

|

|

|

|

| H _D #2 3 |

| M2 3 | D [ 2 2 ] # |

|

| D [ 54 ] # | A E 2 2 | H _ D # 55 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

| H _ A # 2 7 | W 2 | A [ 2 6 ] # |

|

|

| T D I | A B 3 | H _ T D O |

|

|

|

|

|

|

|

|

|

| H _D #2 4 |

| P 2 5 | D [ 2 3 ] # |

|

| D | [ 55 ] # | A F 2 3 | H _ D # 56 |

|

|

|

|

|

|

|

| ||

|

| H_A20M# |

|

|

|

| A [ 2 7 ] # |

|

|

| TD O |

|

|

|

|

|

|

|

|

|

|

| D [ 2 4 ] # |

|

| D [ 56 ] # |

|

|

|

|

|

|

|

| ||||||||||

|

| H_DPSLP# |

|

|

|

| H _ A # 2 8 | W 5 |

|

|

| A B 5 | H _ T MS |

|

|

|

|

|

|

|

|

|

| H _D #2 5 |

| P 2 3 |

|

| A C 25 | H _ D # 57 |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| H _ A # 2 9 | Y 4 | A [ 2 8 ] # |

|

|

| T MS | A B 6 | H _ T R S T # |

|

|

|

|

|

|

|

|

|

| H _D #2 6 |

| P 2 2 | D [ 2 5 ] # |

|

| D | [ 57 ] # | A E 2 1 | H _ D # 58 |

|

|

|

|

|

|

|

| ||

|

| H_IGNNE# |

|

|

|

| A [ 2 9 ] # |

|

|

| TR S T # |

|

|

|

|

|

|

|

|

|

|

| D [ 2 6 ] # |

|

| D [ 58 ] # |

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

| H _ A # 3 0 | U 2 |

|

|

| C 2 0 | I TP _D B R S T # |

|

|

|

|

|

|

|

|

|

| H _D #2 7 |

| T2 4 |

|

| A D 21 | H _ D # 59 |

|

|

|

|

|

|

|

| |||||||

|

| H_SMI# |

|

|

|

| H _ A # 3 2 | W 3 | A [ 3 1 ] # |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| H _D #2 9 |

| L2 5 | D [ 2 8 ] # |

|

| D | [ 60 ] # | A D 23 | H _ D # 61 |

|

|

|

|

|

|

|

| |

|

| H_STPCLK# |

|

|

|

| H _ A # 3 3 | A A 4 | A [ 3 2 ] # |

|

| THERMAL |

|

|

|

|

|

|

|

|

|

|

|

| H _D #3 0 |

| T2 5 | D [ 2 9 ] # |

|

| D | [ 61 ] # | A F 2 2 | H _ D # 62 |

|

|

|

|

|

|

|

| ||

|

| 0.5" < L< | 12" |

|

|

| H _ A # 3 4 | A B 2 | A [ 3 3 ] # |

|

|

|

|

|

|

|

|

|

|

|

|

|

| H _D #3 1 |

| N 2 5 | D [ 3 0 ] # |

|

| D | [ 62 ] # | A C 23 | H _ D # 63 |

|

|

|

|

|

|

|

| |||

|

| CPU TO ICH with same |

|

| H _ A # 3 5 | A A 3 | A [ 3 4 ] # |

|

| P R O C H O T # | D 2 1 | H _ P R O C H OT # |

|

|

|

|

|

|

|

| 5 | H _ D S T B N #1 |

| L2 6 | D [ 3 1 ] # |

|

| D [ 63 ] # | A E 2 5 | H _ D S T B N # 3 | 5 |

|

|

|

|

|

| |||||||

|

| 5 |

| A [ 3 5 ] # |

|

|

|

|

|

|

|

|

|

|

| D S T B N [ 1] # |

| D S T B N [ 3 ] # |

|

|

|

|

|

| ||||||||||||||||||||

|

| ground plane |

| H _ A D S TB # 1 |

| V 1 | A D S T B [ 1] # |

|

| TH E R M D A | A 2 4 | H _ T H E R MD A |

|

|

|

|

|

|

|

| 5 | H _ D S T B P # 1 |

| M2 6 | D S T B P [ 1 ] # |

| D S TB P [ 3 ] # | A F 2 4 | H _ D S T B P # 3 | 5 |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| B 2 5 | H _ T H E R MD C |

|

|

|

|

|

|

|

| 5 H _ D I N V # 1 |

|

| N 2 4 |

| A C 20 | H _ D I N V #3 5 |

|

|

|

|

|

|

| |||||||||

|

|

| <12 in che s | 2 2 | H _ A 2 0 | M# |

| A 6 |

|

| ICH | T H E R MD C |

|

|

|

|

|

|

|

|

|

|

|

|

| D I N V [ 1 ] # |

|

| D I N V [ 3 ] # |

|

|

|

|

|

|

|

| |||||||

22 | H _F | E R R # |

| A 5 | A 2 0 M# |

| T H E R MT R I P # | C 7 | P M _ TH R M TR I P # | 7, 2 2 |

|

| R 41 6 | * 1 K _0 4 | C P U _ TE S T2 | A D 2 6 | T E S T 1 | MISC |

| C O MP [ 1 ] | R 2 6 | C OM P 0 | traces should | be at least 25 | mils | (> | 50 | mils | ||||||||||||||||

|

| 2 2 | H _ I G N N E # |

|

| I G N N E # |

|

|

|

| D 2 5 |

| A A 1 | C OM P 2 | ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| C 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| R 62 |

| * 1 K _0 4 | C P U _ TE S T1 | C 2 3 |

|

|

|

|

| U 2 6 | C OM P 1 |

|

|

|

|

|

|

|

| ||

|

|

|

|

| 2 2 H _ S T P C L K # |

| D 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C P U _ TE S T3 | C 2 4 | T E S T 2 |

|

| C O MP [ 2 ] | Y 1 | C OM P 3 | preferred) away from any other toggling |

| ||||||||||

|

|

|

|

|

| C 6 | S T P C LK # |

|

| H CLK |

|

|

|

|

|

|

|

| C 61 3 | *. 1 U _ 1 0V _ X 7 R _ 04 | C P U _ TE | S T4 | A F 2 6 | T E S T 3 |

|

| C O MP [ 3 ] |

|

| signal. |

|

|

|

|

| |||||||||

|

|

|

|

| 2 2 | H _ I N TR |

| B 4 | L I N T 0 |

|

| A 2 2 | C LK _C P U _ B C L K 2 |

|

|

|

|

|

| C P U _ TE | S T5 | A F 1 | T E S T 4 |

|

| D P R S T P # | E 5 | H _ D P R S TP # 7 , 2 2, 4 1 |

|

|

|

|

| |||||||||||

|

|

|

|

| 2 2 H _ N MI |

|

| A 3 | L I N T 1 |

|

|

| B C LK [ 0 ] | A 2 1 |

|

|

|

|

|

| C P U _ TE S T6 | A 2 6 | T E S T 5 |

|

| B 5 |

|

|

|

|

| |||||||||||||

|

|

|

|

| 2 2 H _ S M I # |

| S M I # |

|

|

| B C LK [ 1 ] | C LK _C P U _ B C L K # 2 |

|

|

|

|

|

| T E S T 6 |

|

| D P S L P # | H _ D P S L P # 2 2 |

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C P U _ TE S T7 | C 3 |

|

| D 2 4 |

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

| C P U R S V D 0 1 | M4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 C P U _B S E L0 |

| B 2 2 | T E S T 7 |

|

| D P W R # | D 6 | H _ D P W R # 5 |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| C P U R S V D 0 2 | R S V D [ 0 1 ] |

|

|

|

|

|

|

|

|

|

|

|

|

|

| B S E L [ 0 ] |

| P W R G OOD | H _ P W R G D 2 2 | H_PWRGD <12" (CPU TO ICH9M) |

|

|

| |||||||||||||||

|

|

|

|

|

| N 5 |

|

|

|

|

|

|

|

|

|

|

|

|

| 2 C P U _B S E L1 |

| B 2 3 |

| D 7 | H _ C P U S LP # 5 |

|

|

| ||||||||||||||||

|

|

|

|

|

| C P U R S V D 0 3 | T2 | R S V D [ 0 2 ] |

| RESERVED |

|

|

|

|

|

|

|

|

|

|

|

| C 2 1 | B S E L [ 1 ] |

|

|

| S L P # | A E 6 |

|

|

|

|

|

| |||||||||

|

|

|

|

|

| C P U R S V D 0 9 | R S V D [ 0 8 ] |

|

|

|

|

|

|

|

|

|

|

|

| 2 C P U _B S E L2 |

| B S E L [ 2 ] |

|

|

| P S I # | P S I # 4 1 |

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

| F 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

| C P U R S V D 0 4 | V 3 | R S V D [ 0 3 ] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| C P U R S V D 0 5 | B 2 | R S V D [ 0 4 ] |

|

|

|

|

|

|

|

|

|

| Layout note: |

|

|

|

| P e n ry n |

|

|

|

|

| TO POWER PAGE |

|

|

|

|

|

|

| |||||||

|

|

|

|

|

| C P U R S V D 0 6 | D 2 | R S V D [ 0 5 ] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

| C P U R S V D 0 7 | D 22 | R S V D [ 0 6 ] |

|

|

|

|

|

|

|

|

|

| Zo=55 ohm, 0.5"max for GTLREF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

| C P U R S V D 0 8 | D 3 | R S V D [ 0 7 ] |

|

|

|

|

|

|

|

| 10mils | C P U _ GT L R E F | R 3 9 2 | 1K _ 1 % _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| R S V D [ 0 9 ] |

|

|

|

|

|

|

|

|

|

|

|

| Layout | note: |

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| placed on the |

|

|

| R 3 94 |

|

|

| 1. 0 5 V S |

|

|

|

| Ohms |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| should | be |

|

|

|

|

|

|

| COMP0, | COMP2: 0.5" Max, Zo=27.4 |

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| no | decoupling |

|

|

|

|

|

|

|

| COMP1, | COMP3: 0.5" Max, Zo=55 | Ohms |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

| P en ry n |

|

|

|

|

|

|

|

|

| GTLREF pin |

|

|

| 2 K _ 1 %_ 0 4 |

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DESIGN GUIDE | P.65 |

|

|

|

|

|

|

| Best estimate is 18 mils wide trace for outer |

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| layers | and 14 mils wide trace if on internal |

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| layers. |

|

|

|

|

|

|

|

|

|

| ||

1 . 0 5V S |

|

|

|

| |

| R 57 | 5 6 _ 04 | H _ I E R R # | ||

| R 32 |

| 5 4 . 9 _1 % _ 04 | H _ P R E Q# |

|

| R 60 |

| 5 6 _ 04 | H _ P R OC H OT # |

|

| R 31 | 5 4 . 9 _1 % _ 04 | H _ T MS | ||

| R 30 |

| 5 4 . 9 _1 % _ 04 | H _ T D I |

|

| R 33 | 5 4 . 9 _1 % _ 04 | H _ T C K | ||

| R 34 |

| 6 4 9 _1 % _0 6 | H _ T R S T # |

|

|

|

|

|

|

|

3 . 3 V S

R 56 |

| * 1K _0 4 | I T P _ D B R S T# |

H _TD I

C irc ul t: 54 .9 o hm ch eck 1 50 oh m

I f P RO CHO T# | i s r ou te d b et wee n | CP U, | IM VP | an d | MC H, |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

p ull | to b e 6 8 | oh m ? | 5 %. | If | n ot |

|

|

|

|

|

|

|

|

|

| C OM P 0 |

|

|

| ||

|

|

|

|

|

|

|

|

|

| C OM P 1 |

|

|

| ||||||||

u se, p ull | res is to r h as | to | b e 56 | oh m | ? 5 % |

| THERMAL SENSER |

|

|

|

|

| C OM P 2 |

|

|

| |||||

|

|

| R 7 0 D 03* 20 m i l s ho rt |

|

|

| V D D 3 |

| EC |

| C OM P 3 | R 2 9 | R 3 9 5 | R 3 9 7 | |||||||

|

|

|

|

|

|

|

| R 2 8 | |||||||||||||

|

|

|

| A- 03 13 |

|

|

|

|

|

|

| NEAR |

|

|

|

|

| ||||

3 . 3 V |

| Q3 |

|

|

|

|

| V _ TH R M |

|

|

|

| 5 4 . 9 _1 % _ 04 | 27 . 4 _ 1% _ 0 4 | 5 4. 9 _ 1 %_ 0 4 | 2 7 . 4_ 1 %_ 0 4 | |||||

|

|

| *A O 34 0 9 |

|

|

|

|

| R 6 5 |

| Z 0 3 06 |

|

|

|

|

|

|

|

| ||

|

|

| S | D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Layout Note: | C 2 2 5 |

|

|

|

|

|

| R 6 4 | C 2 0 1 | 10 K _ 0 4 |

|

|

|

|

| C 2 21 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Within 2.0" |

| Z 0 3 02 | G | R 8 7 | *1 0 0K _ 0 4 | 1 U _ 6 . 3V _ 0 4 |

|

|

| R 6 6 | R 6 9 | R 68 | R 7 4 | *. 1 U _ 1 6V _ 0 4 |

|

|

| ||||

of the CPU | * . 01 U _ 1 6 V _0 4 |

|

|

|

|

|

|

|

| *1 0m i l _s h or t | 4 . 7K _ 0 4 | 4 . 7 K _0 4 | * 1 0K _ 0 4 |

|

|

|

|

| |||

| R 92 |

|

| * 20 K _ 0 4 |

|

|

|

| U 6 |

|

|

|

|

|

|

| T H E R M_ A L E R T # 34 |

|

|

| |

|

| Z 0 3 03 |

|

|

|

|

|

| 1 |

|

| 4 |

|

|

|

|

|

|

|

| |

| * 10 0 K _ 04 |

|

|

| H _ TH E R M D A |

| 2 | V D D | T H E R M | 6 Z 0 3 07 |

|

|

| D 6 | S C S 7 51 V |

|

|

|

| ||

| D |

|

|

|

|

|

| D + | A LE R T |

|

|

|

| C | A | P M _T H R M# 2 4 |

|

|

| ||

|

|

|

|

|

|

|

| C 1 9 8 |

|

| R 67 | *0 _ 0 4 |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| G |

|

|

|

|

|

| 1 00 0 P _ 50 V _ 0 4 |

|

| 7 |

|

|

|

|

|

|

|

|

|

34 T H E R M_ R S T# |

|

|

|

|

|

| 3 | D - | S D A TA |

|

|

| S MD _C P U _ T H E R M 3 4 | 1 4, 1 5 , 2 2, 2 3 , 2 4, 2 5 , 2 6, 2 8 , 3 0, 3 1 , 3 5, 3 7 , 3 8 3 . 3 V | |||||||

|

| Q6 |

| H _ TH E R M D C |

| 5 | 8 |

|

|

| |||||||||||

|

|

|

|

|

| G N D | S C LK |

|

|

| S MC _C P U _ T H E R M 3 4 |

|

| 22 , 3 4 , 35 , 3 6 , 40 V D D 3 | |||||||

|

|

| S | *2 N 7 0 02 W |

|

|

|

|

|

|

|

|

|

|

| 2 , 4 , 5 , 7 , 9, 1 0 , 2 2, 2 5 , 3 7, 3 9 1 . 05 V S | |||||

|

|

|

|

|

|

|

|

|

| W 83 L 7 71 A W G |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 , 6, 7, 1 0 , 12 , 1 3 , 14 , 1 5 , 22 , 2 3 , 24 , 2 5 , 26 , 2 7 , 28 , 2 9 , 30 , 3 1 , 32 , 3 3 , 34 , 3 5 , 39 , 4 1 , 43 3 . 3 V S | |||

| Layout Note: |

|

|

|

| Layout Note: |

| D03B |

|

|

|

|

|

|

|

|

|

| |||

Route H_THERMDA | and | Near to Thermal | |

H_THERMDC on | same layer. | IC | |

10 mil trace | on | 10 mil spacing. |

|

B - 4 Penryn