B.Schematic Diagrams![]()

Schematic Diagrams

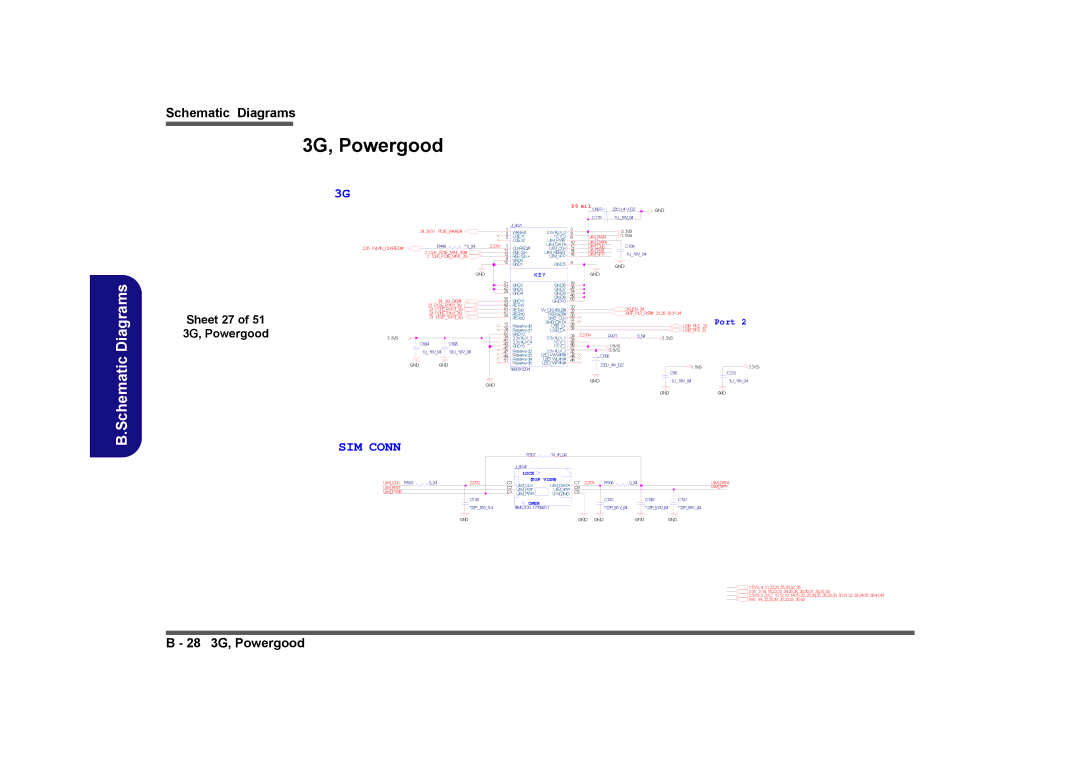

3G, Powergood

3G

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 0 mi l |

|

|

|

| + |

|

| 220 U_4 V_D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C697 |

|

|

|

|

| GND |

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 | J_3G1 |

|

|

| 2 |

|

|

| C179 |

|

| . 1U_16V_04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

| 24, 26,31 PCIE_WAKE# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3. 3VS |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

| 3 | WAKE# | 3.3VAUX_0 | 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 | COEX1 |

| 1.5 V_0 | 8 |

|

|

| UIM_PWR |

| 1. 5VS |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| COEX2 | UIM_PWR | 10 |

|

|

| UIM_DATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

| R448 |

|

|

| *0_04 |

| Z2701 | 7 |

|

|

|

| UIM_DATA | 12 |

|

|

| UIM_CLK |

|

| C199 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

| 2,26 WLAN_CLKREQ# |

|

|

|

|

|

| CLKREQ# | UIM_CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 11 | 14 |

|

|

| UIM_RST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

| 2 CLK_PCIE_MINI_3G# |

|

|

| 13 | REFCLK- | UIM_RESET | 16 |

|

|

| UIM_VPP |

|

| .1U_16V_ 04 |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||

|

|

|

| 2 CLK_PCIE_MINI _3G |

|

|

| 9 | REFCLK+ | UIM_VPP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 15 |

|

|

| 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND1 |

| GND5 |

|

|

|

|

|

|

|

|

|

|

| GND |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| K E Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| GND |

|

|

|

|

|

|

|

|

|

| GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 21 |

|

|

|

|

|

|

| 18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND2 |

| GND6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 27 | GND3 |

| GND7 | 26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 29 |

| 34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND4 |

| GND8 | 40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| 34 3G_DET# |

|

|

|

| 35 |

|

|

|

|

| GND9 | 50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

| 23 | GND11 |

| GND10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

| 23 PCIE_RXN3_3G |

|

|

|

| PETn0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

| 25 |

|

|

| 20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

| 23 PCI E_RXP3_3G |

|

|

|

| 31 | PETp0 | W_DISABLE# | 22 |

|

|

|

|

|

|

|

|

|

|

|

|

| 3G_EN 34 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

Sheet 27 of 51 |

|

|

|

| 23 PCI E_TXN3_3G |

|

|

|

| 33 | PERn0 | PERSET# | 30 |

|

|

|

|

|

|

|

|

|

|

|

|

| BUF_PLT_RST# 23,26, 29,31,34 | Port 2 | |||||||||||||||||||||||||||||

|

|

|

| 23 PCIE_TXP3_3G |

|

|

| 17 | PERp0 | SMB_DATA | 36 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

|

|

|

| SMB_CLK | 32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Reserve d0 |

| USB_D- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| USB_PN2 23 | |||||||||

3G, Powergood |

| 3 .3VS |

|

|

|

|

|

|

|

|

|

|

|

|

| 19 | 38 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 .3VS | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 41 | 3.3VAUX_3 | 3.3VAUX_1 | 28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| USB_PP2 23 |

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 37 | Reserve d1 | USB_D+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 39 | GND12 |

|

|

| 24 Z2704 |

|

|

|

|

|

| R477 | 0_04 |

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3.3VAUX_4 |

| 1.5 V_1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

| C694 |

| C695 |

|

|

| 43 | GND13 |

| 1.5 V_2 | 48 |

|

|

|

|

|

|

|

|

| 1.5VS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 45 |

| 52 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| . 1U_ 16V_04 |

| 10U_10V_08 |

|

|

| 47 | Reserve d2 | 3.3VAUX_2 | 42 |

|

|

|

|

|

|

|

|

| 3.3VS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 49 | Reserve d3 | LED_WWAN# | 44 |

|

|

| + |

| C696 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 51 | Reserve d4 | LED_WLAN# | 46 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| GND |

|

| GND |

|

|

|

|

|

|

|

|

| Reserve d5 | LED_WPAN# |

|

|

|

|

|

|

|

| 220U_4V_D2 |

|

|

|

|

|

|

|

| 1. 5VS |

|

|

| 3.3VS | |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C66 |

|

|

|

| C213 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| .1U_16V_04 |

|

| . 1U_16V_04 | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND |

|

| GND | ||||||

| SIM CONN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R507 |

| *4. 7K_04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| J_SI M1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| UIM_CLK R503 | 0_04 |

|

|

|

|

| Z2702 |

|

|

| C3 |

| (TOP VIEW) |

| C7 | Z2703 |

| R508 | 0_04 |

|

|

|

|

|

|

|

|

|

|

| UIM_DATA | ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| UIM_CLK | UIM_DATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| UIM_RST |

|

|

|

|

|

|

|

|

|

|

|

|

|

| C2 |

|

| C6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| UIM_VPP | ||||||||||

|

| UIM_PWR |

|

|

|

|

|

|

|

|

|

|

|

|

| C1 |

| UIM_RST |

| UIM_VPP |

| C5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| UIM_PWR |

| UI M_GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| C7 35 |

|

|

|

|

| OPEN |

|

|

|

|

|

|

|

|

|

|

|

| C742 |

|

|

|

|

|

|

| C740 |

|

|

|

|

| C737 |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| *22P_50V_0 4 |

|

| SIMLOCK |

|

|

|

|

|

|

|

|

| *22P_50V_04 |

| *22P_5 0V_04 |

| *22P_50V_04 |

|

|

|

| ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| GND |

|

|

|

|

|

|

|

|

|

|

|

| GND |

|

| GND |

|

|

|

|

|

|

| GND |

|

|

|

|

| GND |

|

|

|

|

|

| ||||||||||||

1.5VS 4 | ,10,22,23 ,25,26,32 ,35 | |

3.3V | 3,14, 15,22,23, 24,25,26, 28,30,31, 35,37,38 | |

3.3VS 2 | ,3,6,7, 10,12,13, 14,15,22, 23,24,25, 26,28,29, 30,31,32, 33,34,35, 39,41,43 | |

5VS 14, | 22,25,28, 30,32,33, 35,43 | |

B - 28 3G, Powergood