CY7C1146V18, CY7C1157V18

CY7C1148V18, CY7C1150V18

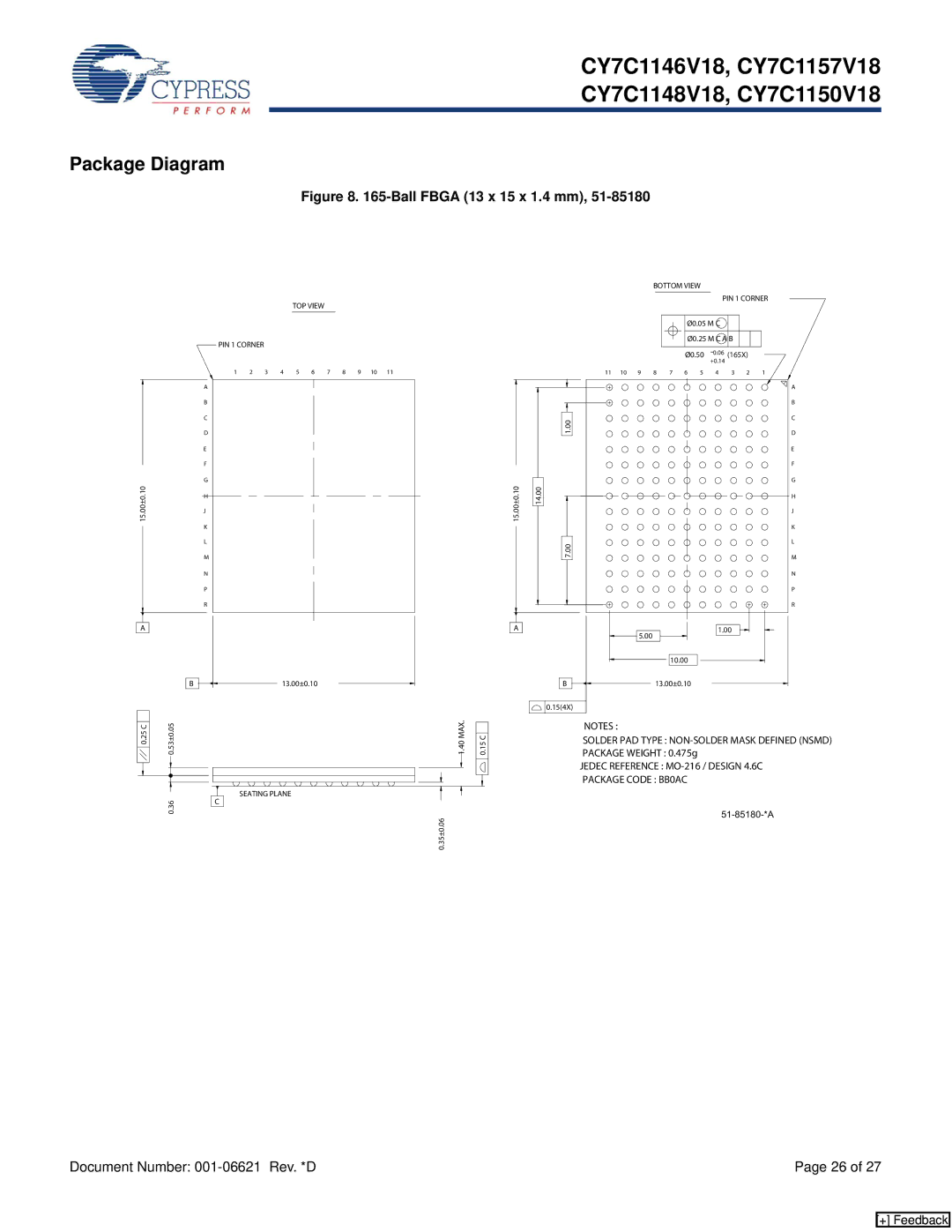

Package Diagram

Figure 8. 165-Ball FBGA (13 x 15 x 1.4 mm), 51-85180

15.00±0.10

A

TOP VIEW

PIN 1 CORNER

1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

15.00±0.10

A

BOTTOM VIEW

|

|

|

|

|

|

| PIN 1 CORNER | |||

|

|

|

|

| Ø0.05 M C |

|

|

| ||

|

|

|

|

|

| Ø0.25 M C A B |

|

| ||

|

|

|

|

| Ø0.50 | (165X) |

| |||

|

|

|

|

|

|

| +0.14 |

|

|

|

11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|

|

|

|

|

|

|

|

|

| A |

|

|

|

|

|

|

|

|

|

| B |

1.00 |

|

|

|

|

|

|

|

|

| C |

|

|

|

|

|

|

|

|

| D | |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| E |

|

|

|

|

|

|

|

|

|

| F |

14.00 |

|

|

|

|

|

|

|

|

| G |

|

|

|

|

|

|

|

|

| H | |

|

|

|

|

|

|

|

|

|

| J |

|

|

|

|

|

|

|

|

|

| K |

7.00 |

|

|

|

|

|

|

|

|

| L |

|

|

|

|

|

|

|

|

| M | |

|

|

|

|

|

|

|

|

|

| |

N

P

R

1.00 |

5.00 |

10.00 |

0.25 C

| B |

0.53±0.05 |

|

0.36 | C |

|

13.00±0.10

|

| 1.40MAX. |

|

|

|

|

|

|

|

| |||

| 0.15C | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SEATING PLANE

0.35±0.06

B ![]()

![]()

![]() 13.00±0.10

13.00±0.10

0.15(4X)

NOTES :

SOLDER PAD TYPE :

PACKAGE WEIGHT : 0.475g

JEDEC REFERENCE :

Document Number: | Page 26 of 27 |

[+] Feedback