CY7C1303BV25

CY7C1306BV25

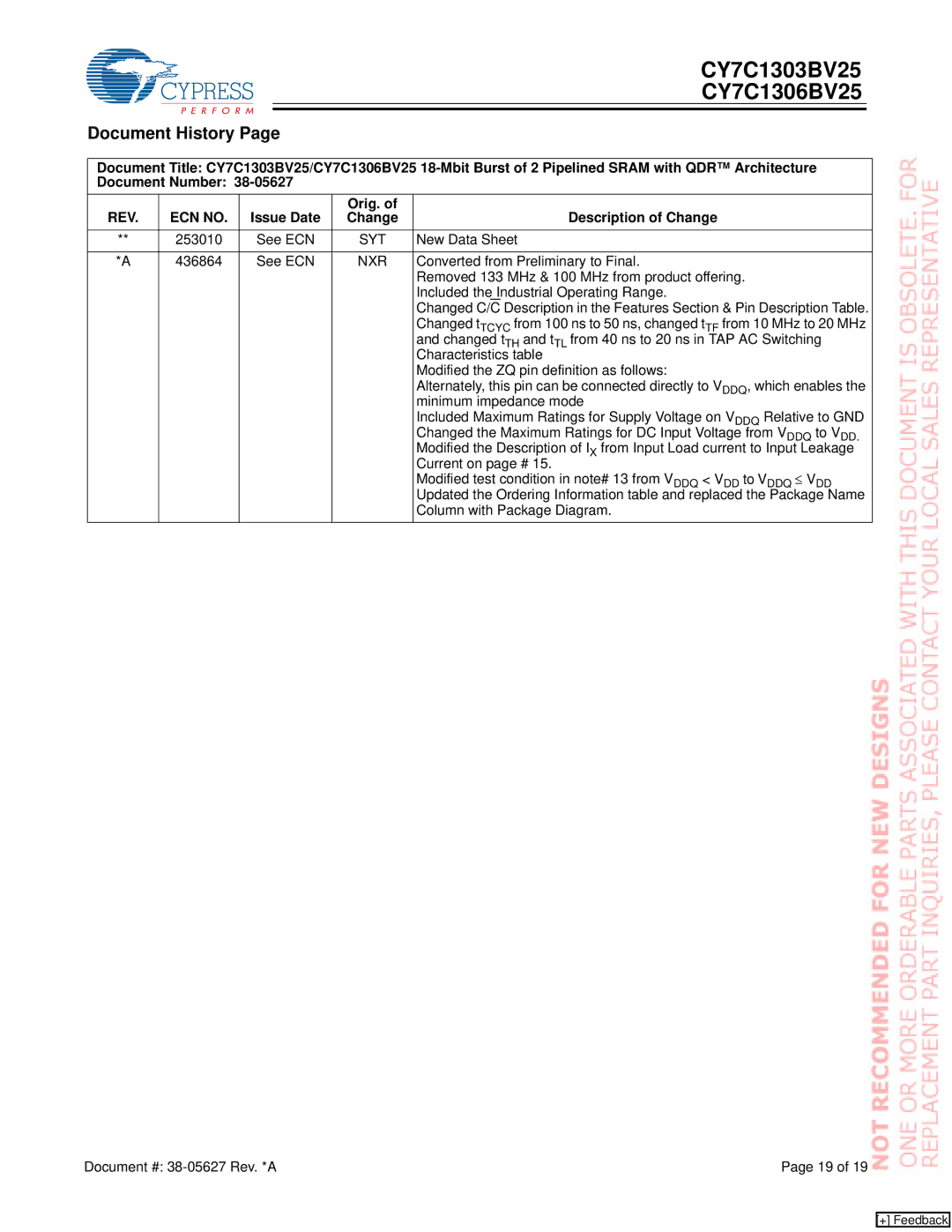

Document History Page

Document Title: CY7C1303BV25/CY7C1306BV25

Document Number:

REV. | ECN NO. | Issue Date | Orig. of | Description of Change |

Change | ||||

|

|

|

|

|

** | 253010 | See ECN | SYT | New Data Sheet |

|

|

|

|

|

*A | 436864 | See ECN | NXR | Converted from Preliminary to Final. |

|

|

|

| Removed 133 MHz & 100 MHz from product offering. |

|

|

|

| Included the Industrial Operating Range. |

|

|

|

| Changed C/C Description in the Features Section & Pin Description Table. |

|

|

|

| Changed tTCYC from 100 ns to 50 ns, changed tTF from 10 MHz to 20 MHz |

|

|

|

| and changed tTH and tTL from 40 ns to 20 ns in TAP AC Switching |

|

|

|

| Characteristics table |

|

|

|

| Modified the ZQ pin definition as follows: |

|

|

|

| Alternately, this pin can be connected directly to VDDQ, which enables the |

|

|

|

| minimum impedance mode |

|

|

|

| Included Maximum Ratings for Supply Voltage on VDDQ Relative to GND |

|

|

|

| Changed the Maximum Ratings for DC Input Voltage from VDDQ to VDD. |

|

|

|

| Modified the Description of IX from Input Load current to Input Leakage |

|

|

|

| Current on page # 15. |

|

|

|

| Modified test condition in note# 13 from VDDQ < VDD to VDDQ ≤ VDD |

|

|

|

| Updated the Ordering Information table and replaced the Package Name |

|

|

|

| Column with Package Diagram. |

Document #: | Page 19 of 19 |

[+] Feedback