CY7C1470V33

CY7C1472V33

CY7C1474V33

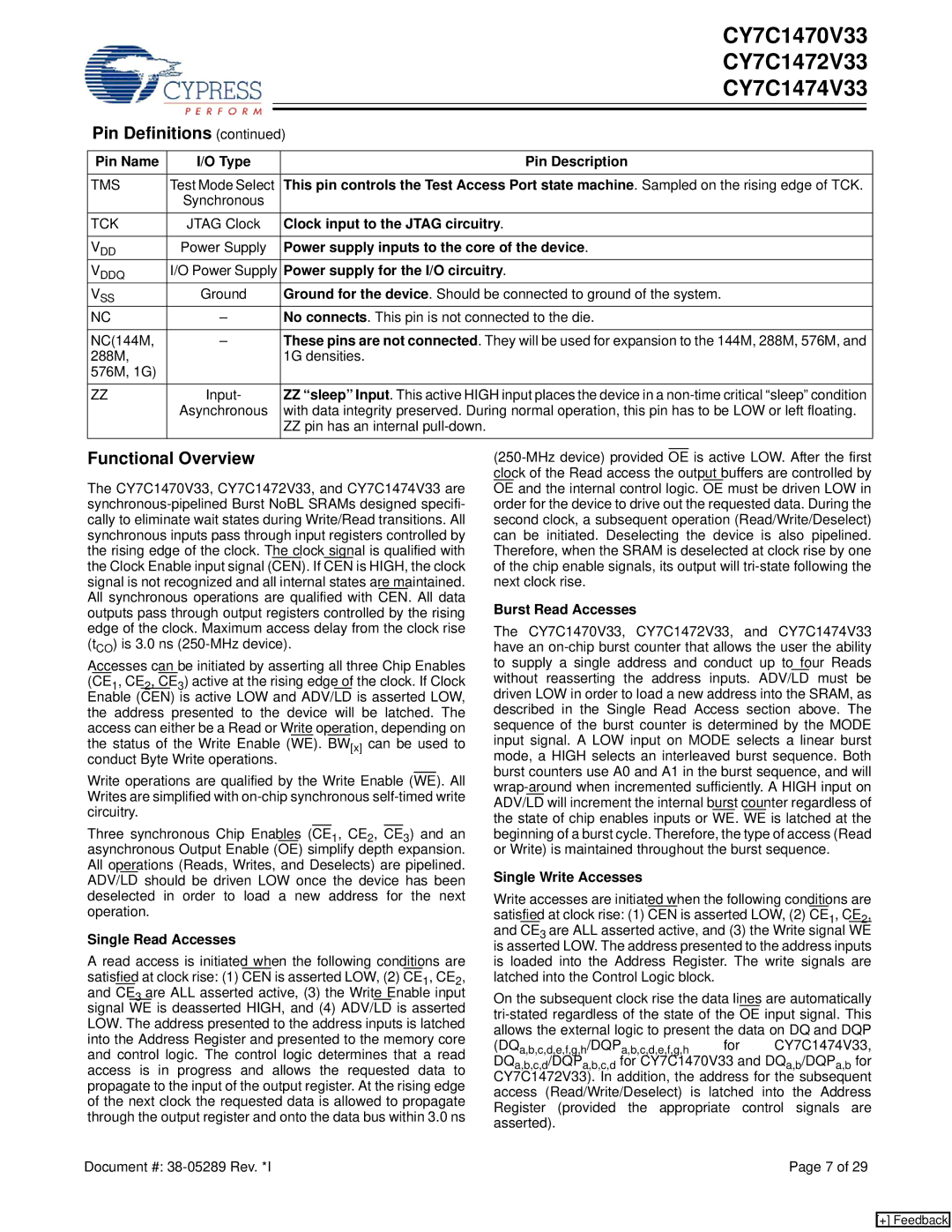

Pin Definitions (continued)

Pin Name | I/O Type | Pin Description |

|

|

|

TMS | Test Mode Select | This pin controls the Test Access Port state machine. Sampled on the rising edge of TCK. |

| Synchronous |

|

TCK | JTAG Clock | Clock input to the JTAG circuitry. |

|

|

|

VDD | Power Supply | Power supply inputs to the core of the device. |

VDDQ | I/O Power Supply | Power supply for the I/O circuitry. |

VSS | Ground | Ground for the device. Should be connected to ground of the system. |

NC | – | No connects. This pin is not connected to the die. |

|

|

|

NC(144M, | – | These pins are not connected. They will be used for expansion to the 144M, 288M, 576M, and |

288M, |

| 1G densities. |

576M, 1G) |

|

|

ZZ | Input- | ZZ “sleep” Input. This active HIGH input places the device in a |

| Asynchronous | with data integrity preserved. During normal operation, this pin has to be LOW or left floating. |

|

| ZZ pin has an internal |

Functional Overview

The CY7C1470V33, CY7C1472V33, and CY7C1474V33 are

Accesses can be initiated by asserting all three Chip Enables (CE1, CE2, CE3) active at the rising edge of the clock. If Clock Enable (CEN) is active LOW and ADV/LD is asserted LOW, the address presented to the device will be latched. The access can either be a Read or Write operation, depending on the status of the Write Enable (WE). BW[x] can be used to conduct Byte Write operations.

Write operations are qualified by the Write Enable (WE). All Writes are simplified with

Three synchronous Chip Enables (CE1, CE2, CE3) and an asynchronous Output Enable (OE) simplify depth expansion. All operations (Reads, Writes, and Deselects) are pipelined. ADV/LD should be driven LOW once the device has been deselected in order to load a new address for the next operation.

Single Read Accesses

A read access is initiated when the following conditions are satisfied at clock rise: (1) CEN is asserted LOW, (2) CE1, CE2, and CE3 are ALL asserted active, (3) the Write Enable input signal WE is deasserted HIGH, and (4) ADV/LD is asserted LOW. The address presented to the address inputs is latched into the Address Register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the rising edge of the next clock the requested data is allowed to propagate through the output register and onto the data bus within 3.0 ns

Burst Read Accesses

The CY7C1470V33, CY7C1472V33, and CY7C1474V33 have an

Single Write Accesses

Write accesses are initiated when the following conditions are satisfied at clock rise: (1) CEN is asserted LOW, (2) CE1, CE2, and CE3 are ALL asserted active, and (3) the Write signal WE is asserted LOW. The address presented to the address inputs is loaded into the Address Register. The write signals are latched into the Control Logic block.

On the subsequent clock rise the data lines are automatically

(DQa,b,c,d,e,f,g,h/DQPa,b,c,d,e,f,g,h for CY7C1474V33, DQa,b,c,d/DQPa,b,c,d for CY7C1470V33 and DQa,b/DQPa,b for CY7C1472V33). In addition, the address for the subsequent access (Read/Write/Deselect) is latched into the Address Register (provided the appropriate control signals are asserted).

Document #: | Page 7 of 29 |

[+] Feedback